Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИИЛЬСМЭУ

Союз Советских

Социалистических

Респубпии (1l) 585д4g (6l) Дополнительное к авт. саид-ву (22) Заявлено 19.05.76 (21) 2362769/18-2 с присоединением заявки № (23) Приоритет (53) M. Кл.

Q 11 С 17/02

Гееударвтееинмв евметет

Сввете Меилетров СССР ве делам езобретенюе я еткрытей (43) ОпУбликовано 25, 12. 77 Бюллетень И.47 (5З) >Д 628,Э27..6 (088.8) (45) Дата опубликования описания 15.i2..77 (72) Авторы изобретения

А. М. Селигей и Q. С. Тросгянецкий (71) Заявитель

Киевский ордена Трудового Красного Знамени завод электронных вычислительных и управляющих машин (54) ПОСТОЯННОЕ ЗА ПОМИНА ЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам, и может быть использовано в вычислительной технике и автоматике. Известно постоянное запоминающее устройство, содержащее основные и дополнительные запоминающие трансформаторы, прошитые кодовыми проводами и подключенные к дешифратору, и элементы ИЛИ, одни входы которых соединены с выходиыми обмотками основных запоминающих трансформаторов 11).

Дополнительные запоминающие трансформаторы предназначены для занесения в них базовых кодов.

Недостатком устройства является сравнительно небольшой набор независимых базовых кодов. Если кодовый провод последовательно прошивает несколько дополнительных запоминающих трансформаторов, то образуется составной базовый код как дивъюнкция нескольких базовых кодов. Зависимость составного базового кода от ранее выбранных базовых кодов (количество которых равно количеству дополнительных запоминающих трансформаторов) ограничивает возможности увеличения информационной емкости устройства.

Цель изобретения — увеличить информационную емкость устройства.

Это достигается тем, что устройство содержит дополнительный дешифратор, выходы которого подключены к другим входам соответствующих элементов ИЛИ, а входы — к выходным обмоткам дополнительных запоминающих трансформаторов.

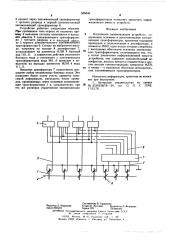

На чертеже приведена схема устройства.

Устройство содержит и основных запоминаеащих трансформаторов l, прошитых кодовыми проводами 2. Выходные обмотки 3 зйпоминаю ч щих трансформаторов 1 подключены к одним входам элементов ИЛИ 4 в каждом разряде, а выходные обмотки 5 дополнительных запоминающих трансформаторов 6 — ко входан дополнительного дешифратора 7.

Каждый кодовый провод 2 последовательно прошивает трансформаторы 1 и 6, причем количество трансформаторов 6 может белти раэличным (в качестве примера показаМЬ т1ен трансформатора) .

20 к»

Дешифратор 7 формирует 2 -1 независимых базовых кодов, где к — количество донолнительных запоминающих трансформаторов,6.

При возбуждении выхода 8 дешифратора 7 устанавливается базовый код 110...0, Для эанервсения, например кода 111...0, кодовый провод

Ъ

2 прошит через запоминающий трансформатор

I третьего разряда и первый дополнительный запоминающий трансформатор 6.

Устройство работает следующим образом.

Ирн протекании тока опроса по кодовому проаоАу 2 выходные сигналы появляются в выход4е@й обмотке 3 запоминающего трансформатора 1 третьего разряда и в выходной обмотке 5 первого дополнительного запоминающего трансформатора 6. Сигнал на выбранном выходе, например на выходе 8 дешифратора 7, устанавливает на влементах ИЛИ 4 базовый код 110...0, а совместное действие указанного базового кода и считанного с запомилающих трансформаторов кода 001...0 приводит к появлению на выходах элементов ИЛИ 4 кода

111...0.

Введение дешифратора 7 существенно расширяет набор независимых базовых кодов. Это позволяет более полно учесть характер заносимой 14нформации, уменьшить число проводов, прошиваемых через основные запоминающие трансформаторы 1 и, следовательно, пря тех же размерах сердечников запоминающих

585546 трансформаторов позволяет увеличить ин<рор мационную емкость устройств.

Формула изобретения

S Постоянное запоминающее устройств.:, содержащее основные и дополнительные запоминающие трансформаторы, прошитые кодовыми проводами и подключенные к дешифратору„н элементы ИЛИ, одни входы которых соединены с выходными обмотками основных запоминаю щих трансформаторов, отличающееся тем, что, с. целью увеличения информационной емкости устройства, оно содержит дополнительный дешифратор, выходы которого подключены к другим. входам соответствующих элементов ИЛИ, 4в а входы — к выходным обмоткам дополнительных запоминающих трансформаторов.

Источники информации, принятые во внимание при экспертизе: !. Авторское свидетельство по заявке № 2336238/18 — 24, кл. G 1 С 17/02, I 7.03.76..

Составнтель В. Гордонова

Редактор Л. Народная Текред О. Луговая Корректор Л. Федорчук

Заказ 5055 42 Тнраж 729 Подписное

ЦНИИПИ Государственного коиитета Совета Министров СССР по лвлан изооретеиии и открытий!!3035, Москва, Ж-З5, Рыушская нвб., л. 4/5

Филиал Г1ПП «Патент», г. Ужгород, ул. Проектная, 4