Устройство для кодирования двоичных циклических кодов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик (ll),585600 (61) дополнительное к авт. свид-ву ю335691 (22) Заявлено 0310.75(21) 2182868/09 с присоединением заявки Pk— (23) Приоритет(43) Оттубликовано 25.12.77. Втоллетеиь ph 47 (45) Дата опубликования описанк Ф 26й2 77 (5l} М. Кл.

03 Z 13/00//

//Э 06 Р ll/12

ГВВ)4Вротоооныб Воаотот

Соввто МВВВВтров СССР

Во 4ВВВа Вообротоооб

В открытой (53) УДК 681.326 . 7 (088. 8) (72) Авторы изобретения

А.Г,Орлов и Л.М.Чебулаев

Pl) Заявитель (54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ДВОИЧНЫХ

ЦИКЛИЧЕСКИХ КОДОВ

Изобретение относится к,технике телеуправления и передачи дискретной информации и может использоваться пре« имущественно для кодирования информации телеуправления, телеконтроля и телесигналиэации.

По основному авт. св. Р 335691 известно устройство для кодирования двоичных циклических. кодов, содержащее сдвигающий сумматорами по модулю два, запоминающий регистр и элементы

И, причем один вход каждого элемента

И соединен с выходом соответствующегО разряда запоминающего регистра, другой

Вход каждого элемента И соединен с выходом сумматора по модулю два, включенного на выходе старшего разряда сдвигающего регистра, выходы элементов И, кроме первого, соединены с входом соответствующего сумматора по модулю два, включенного на выходе предшествующего разряда сдвигающего регистра, а выход первого элемента И

Соединен с входом сдвигающего регистра.

Однако в этом устройстве не предусмотрена воэможность формирования различных классов смежных циклических кодов, что снижает качественные характеристики систем, использующих для передачи информации циклические коды .

Цель изобретения — обеспечение возможности дополнительного формирования различных классов смежных циклических кодов.

Для этого в устройство для кодирования двоичных циклических кодов, содержащее сдвигающий регистр со

10 встроенными сумматорами по модулю два, запоминающий регистр и элементы И, ПРичеМ оДин вХоД Каждсго элемента И соединен с выходом соответствующего разряда запоминающего регистра, другой вход каждого элемента и соединен с выходом сумматора по модулю два, включенного на. выходе старшего разряда сдвигающего регистра, выходы элементов И, кроме первого, соединеяр ны с входом соответствующего сумматора по модулю два, включенного на выходе предшествующего разряда сдвигающего регистра, а выход первого элемента И соединен с входом сдвигаю25 щего регистра, введены элементы И, ИЛИ, НЕ, при этом входы первых элементов И и НЕ соединены с выходом сдвигающего регистра, а входы вторых элементов И и НЕ соединены с вы30 ходом элемента ИЛИ, на входы которогс

585600 поданы ненулевые тактовые импульсы, а выход первого элемента НЕ подключен к второму входу второго элемента И, выход второго элемента НЕ подключен к второму входу первого элемвн» т а И, выходы элементов И подключены к входам второго элемента ИЛИ.

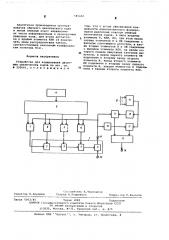

На чертеже изображена структурная электрическая схема устройства для кодирований двоичных циклических к дов.

Предлагаемое устройство для кодирования двоичных циклических кодов содержит сдвигающий регистр 1 co встроенными сумматорами 2, 3, 4, 5 по модулю два, запоминающий регистр 6 и элементы И 7,8,9,10, причем один вход каждого элемента И соединен с выходом соответствующего разряда запоминаю щего оегистра 6, другой вход каждого элемента И соединен с выходом сумматора 5 по модулю два, включенного на ныходе старшего разряда сдвигающего регистра 1, выходы элементов И

8, 9, 10, кроме первого И 7, соединены с входом соответствующего сум- 95 магора 2, 3, 4 по модулю дна, включенного на выходе предшествующего разряда сднигающего регистра 1, а выход первого элемента И 7 соединен с входом сдвигающего регистра элв- 3() менты И 11 12, ИЛИ 13, 14, НЕ 15, 16, при этом входы первых элементов

И ll u HE 15 соединены с выходом сднигающвго регистра 1, а входы нторых элементов И 12 и НЕ 16 соединены 85 с выходом элемента ИЛИ 14, на входы которого поданы нулевые тактовые импуль=ы, а выход первого элемента НЕ

15 подключен к второму входу второго элемента И 12, ныход второго элемен- 41 та HE 16 подключен к второму входу первого элемента И 11, выходы элементов И 11, 12 подключены к входам второго элемента ИЛИ 13. Кроме того, устройство кодиронания содержит запоминающее устройство 17, шину 18 выхода информации (в ниде смежного циклического кода), шину 19 выхода информационных посылок (в виде обычного циклического кода), шину 20 выхода информационных посылок без избыточности, шину 21 выхода ненулевых тактов распределителя тактон.

Предложенное устройство Работает следующим образом.

Информационные посылки безызбыточно-(В го кода поступают на шину 19 регистра

1, содержащего встроенные сумматоры

2, 3, 4, 5 по модулю два. В соотнет« ствии со значениями коэффициентов полинома, образующего данный циклн- ф ческий код P (х), записанный в запоминающее устройство 17 и представленный н нид И-раз(ядного числа в запоминающем регистре 6, на вход

"xeM H 7, 8, 9, 10 поступают сигналы переключения цепей обратной связи регистра 1. Происходит наращивание

И информационных разрядов кода Н -И проверочными Я (х), которые образуются и результате деления полинома информационной части кода Р(х), умноженного íà х на .олином, обрей-N зующий данный циклический код Р(х).

В результате получаем полином кодовой комбинации обычного циклического кода (э(Ъ - (х) . х +) (х) .

Смежные классы циклических кодов могут быть образованы путем сложения по модулю два полинома исходной кодовой комбинации 6 (x) с некоторым преобразующим полиномом Н (х), не равным полиномам разрешенных комбинаций. С целью преобразования импульсы распределителя тактов устройства декодирования информации поступают на входы элемента ИЛИ 14, Поскольку новый результат может быть получен только при ненулевых значениях преобразующего полинома, то на входы элемента ИЛИ 14 подаются только ненулевые тактовые импульсы распределителя тактов. С выхода элемента ИЛИ 14 ненулевые тактовые импульсы поступают на входы элементон И 12 и НЕ 16. С выхода элемента НЕ 16 в инвертированном виде ненулевые тактовые импульсы поступают на вход элемента И 11.

Информационные импульсы с шины 19 выхода подаются на входы элементов

И 11 и НЕ 15. С выхода элемента НЕ

15 информационные импульсы поступают на вход элемента И 12. При отсутстнии ненулвных разрядов преобразующего полинома, что соответстнует передаче обычного циклического кода, сигнал не поступает на вход элемента ИЛИ 14, в результате чего элемент

И 12 оказывается запертым, а с выхода элемента НЕ 16 на вход элемента И 11 поступает сигнал в течение всего времени передачи кодовой комбинации. В этом случае информация без преобразования через элементы

И 11 и ИЛИ 13 поступает на шину 18 выхода.

При ненулевом значении преобразующего полинома, например Н(х) = 1, при передаче всех разрядон кода, кроме последнего, на вход элемента И 11 поступает разрешающий сигнал, а на вход элемента И 12 — запрещающий.

При передаче последнего разряда кода на вход элемента ИЛИ 14 поступает сигнал, который через элемент НЕ 16 запрещает прохождение информационных посылок через элемент И 11 и разрешает через элемент И 12, на второй вход которого через элемент НЕ 15 подается информационная посылка последнего разряда кода.

sH5600

Формула и э обретен и я

Сос> авйтель A.Черепанов

Текред Н.Андрейчук

Корре-;тор С. Ямалова

Редактор Н.Хлудова

Закаэ 5062/45 Тираж 10б5 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР

« д«ам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Аналогично производится преобраэование обычного циклического кода в любой смежный класс независимо от числа информационных и проверочных разрядов кода, для этого достаточно к входам элемента ИЛИ 14 подключить шины распределителя тактов, I соответствующие ненулевым коэффициентам полинома Н(х).

Устройство для кодирования двоичных циклических кодов по авт. св.

В 335691, о т л и ч а ю щ е е с я тем, что с цепью обеспечения воэможности дополнительного формирования различных классов смехных циклических кодов, в него введены элементы И, ИЛИ, НЕ, при этом входы первых элементов И и НЕ соединены q выходом сдвигающего регистра| а входы вторых элементов И и НЕ соединены с выходом элемента ИЛИ, на входы которого поданы ненулевые тактовые импульсы, а выход первого элемента НВ подключен к второму входу второго элемента И, выход второго элемента

НЕ подключен к второму входу первого !

5 элемента И, выходы элементов И подклю+ чены к входам второго элемента ИЛИ.