Цифровой омметр

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 19.11.75 (21) 2192896/18-21 с присоединением заявки Ме (23) Приоритет (43) Опубликовано 30.12.77. Бюллетень Уе 48 (45) Дата опубликования описания 23.12.77 (51) М Кл з б 01К 27/00

Государственный комитет

Совета Министров СССР (53) УДК 621.317.3 (088,8) ло делам изобретений и открытий (72) Автор изобретения

В. С. Гутн и ко в

Ленинградский ордена Ленина политехнический институт им. М, И. Калинина (71) Заявитель (54) ЦИФРОВОЙ OMMETP

Изобретение относится к области измерительной техники и мо кет найти применение при построении цифровых приборов для измерения электрических сопротивлений и неэлектрических величин, воспринимаемых резистивными первичными преобразователями, Известен цифровой омметр, основанный на последовательном интегрировании в течение двух тактов падений напряжения, создаваемых одним током на измеряемом и образцовом сопротивлениях. (1)

Недостаток этого омметра заключается в относительной сложности аналоговой части, содержащей трехпозиционные переключатели и буферный усилитель, что к тому же снижает точность измерения.

Цель изобретения — упрощение устройства и повышение точности измерения.

Достигается цель тем, что в цифровом омметре, содержащем управляющий блок, соединенный с цифровым блоком, нуль-органом и первым ключом, связанным с неинвертирующим входом усилителя интегратора, с конденсатором и через нуль-орган — с выходом упомянутого усилителя интегратора, а также источник питания, подключенный к последовательно соединенным образцовому резистору и измеряемому сопротивлению, причем выводы образцового резистора через второй ключ и выводы измеряемого сопротивления через третий ключ подсоединены к управляющему блоку, предлагается вход интегратора связать с0 вторым ключом, а неинвертирующпй вход усилителя интегратора

5 через конденсатор соединить с третьим ключом.

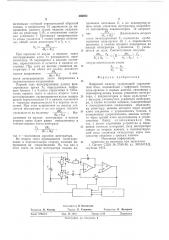

Структурная схема предлагаемого цифрового оммстра показана на чертеже.

Она включает в сеоя цифровой блок 1, уп10 равляющнй блок 2, источник питания 3, к которому присоединены последовательно включенные образцовый 4 и измеряемый 5 резисторы. Зажимы образцозого резистора 4 через переключатель 6 присоединены ко входу

15 интегратора, состоящего из двухвходового усилителя 7, резистора 8 и конденсатора 9, К выходу интегратора присоединен нуль-орган 10. Неппвсртпрующий вход усилителя 7 через ключ 11 соединен с выходом нуль-ор20 гана и через конденсатор 12 и переключатель

13 с зажимами измеряемого резистора 5, Управляющий блок 2 имеет входы, соединяющие его с цифровой частью и выходом нульоргана 10, и выходы, по которым производит25 ся управление цифровой частью, ключом 11 и переключателями 6 и 13.

Исходно, в паузе между измерениями ключ 11 замкнут, а переключатели 6 и 13 находятся в нижнем положении. При этом

30 усилитель 7 и нуль-орган 10 оказываются ох3 ваченными глубокой отрицательной обратной связью, и конденсатор 12 заряжается до напряжения, равного сумме падения напряжения на резисторе 5 R., и напряжения смещения усилителя 7. Потенциал инвертирующего входа усилителя 7 станет равным потенциалу общей точки резисторов 4 и 5, т. е. ек, (Ro + R»)

При переходе от паузы к червому такту интегрирования ключ 11 размыкается, переключатель 13 переводится в верхнее состояние, переключатель 6 остается в нижнем состоянии. Прп этом на выходе усилителя интегратора и на обоих его входах возникнет ек, скачок напряжения и нач(о+ R») нется интегрирование этого напряжения в положительном направлении.

Первый такт интегрирования длится фиксированное время То, определяемое цифровым блоком 1 и блоком управления 2. Окончание первого такта и начала второго такта интегрирования осуществляется путем возвращенпя переключателя 13 в нижнее положение и перевода переключателя 6 в верхнее положение. При этом напряжение на выходе усилителя интегратора и на его входах скачком

ER уменьшается на величину Ha(Ro+ R») пряжение на выходе интегратора в начале второго такта будет равно накопленному в течение первого такта интегралу

ТО Ек» .(R» +.Ro) где т — постоянная времени интегратора.

Во втором такте производится интегрирование в отрицательную сторону падения напряжения на сопротивлении Ro, так как в этом такте на вход интегратора подано на4 пряжение источника Е, и на неинвертирующем входе усилителя интегратора сохраняется запомненное конденсатором 12 напряжеЕ » ние — Длительность второго

5 (R +R,) такта интегрирования Т ограничена срабатыванием нуль-органа 10, т. е. определяется временем, в течение которого напряжение на выходе интегр атора (усилителя 7) умень10 шится до нуля. Соответственно получим

ER, т, / ЕК, т» к, + к„ к,, —,- к,,/ откуда окончательно имеем

15 Т»- R»

7o Ro

Формула изобретения

Цифровой омметр, содержащий управляющий блок, соединенный с цифровым блоком, нуль-органом и первым ключом, связанным с

HeèHâåðTHðóþùèì входом усилителя интегра25 тора, с конденсатором и через нуль-орган— с выходом упомянутого усилителя интегратора а также источник питания, подключенный к последовательно соединенным образцовому резистору, выводы которого через второй

80 ключ соединены с управляющим блоком, и измеряемому сопротивлению, выводы которого через третий ключ подсоединены к управляющему блоку, отличающийся тем, что, с целью упрощения устройства и повы35 шения точности пзмерения, вход интегратора связан со вторым ключом, а неинвертируюший вход усилителя интегратора через конденсатор соединен с третьим ключом.

Источники информации, 40 принятые во внимание при экспертизе

1, Патент США № 3750146, кл. 340/347АД, опублик. 1973.

Редактор Н. Коляда

Заказ 2784/13

Подписное

Изд. № 1010

Тираж 1109

Составитель О. Богомолов

Техред Л. Гладкова

Типография, пр. Сапунова, 2

Корректор H. Федорова