Усилитель считывания для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

"1111 586497

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соеетских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 21.07.75 (21) 2159441/18-24 с присоединением заявки 1че— (23) Приоритет (43) Опубликовано 30.12.77. Бюллетень Хе 48 (45) Дата опубликования описания 25.01.78 (51) М. Кл G 11С 17/00

Государственный комитет

Совета Фйинистров СССР ло левам нзобретс--,ай а открыт."и (53) УДК 681.327.6 (088.8) (72) Авторы изобретения

А. И. Бахир и В, И. Лешукович (71) Заявитель (54) усилитель считывАния для постоянного

ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

Изобретение относится к вычислительной технике и мо."кет быть применено в блоках памяти ЦВМ, в частности в трансформаторных постоянных запоминающих устройствах.

Известны усилители (1, 2), содержащие линейный дифференциальный каскад.

Недостатком этих усилителей при использовании их в разрядной цепи постоянных запоминающих устройств (ПЗУ) трансформаторного типа является то, что время восстановления исходного магнитного состояния возбужденных разрядных сердечников определяется прежде всего пассивными элементами— индуктивностыо выходной обмотки и входным сопротивлением усилителя. Это время превосходит время опроса в 3 — 5 раз, Наиболее близок по техническому решению к изобретению усилитель считывания для постоянного запоминающего устройства (3), содержащий линейный дифференциальный каскад с нагрузочными резисторами на входе и источником смещения, подключенным в общую точку соединения резисторов. Недостаток этого усилителя также заключается в низком быстродействии.

Цель изобретения — уменьшение времени восстановления разрядной цепи ПЗУ и повышение его быстродействия.

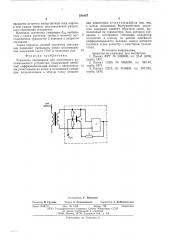

Это достигается тем, что усилитель содержит элемент обратной связи, выполненный на транзисторе, база которого соединена с источником смещения, коллектор подключен к одному из входов линейного дифференциального каскада, выход которого соединен через резистор с эмиттером транзистора.

Схема предлагаемого усилителя приведена на чертеже. (Для пояснения работы на этом же чертеже показаны входная и выходная обмотки разрядного сердечника).

10 Усилитель содержит нагрузочные резисторы

1, транзистор 2, линейный дифференциальный каскад 3, токозадающий резистор 4 и источник смещения Е,„.

Работает усилитель следукпцнм образом.

15 В исходном состоянии благодаря источнику смещения Е,„транзистор 2 заперт. Во время действия сигнала опроса транзистор еще больше смещается в область отсечки, а по окончании сш нала опроса на нагрузочных резисторах

20 1 появляется сигнал обратной полярности. Под действием этого сигнала, усиленного линейным дифференциальным каскадом 3, транзистор 2 открывается и по цепи Е,„, — параллельное соединение нагрузочных резисторов

25 1 — переход коллектор — эмиттер транзистора2 — токозадающий резистор 4 — выход линейного дифференциального каскада 3 протекает ток.

Ампер-витки тока, протекающего через вы30 ходную обмотку разрядного сердечника. на586497

7 к

pnprica

Составитель Г. Мамджян

Редактор И. Грузова Техред А. Камышникова Корректор Т. Добровольская

Заказ 3168/12 Изд. № 1026 Тираж 738

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2 йравлены встречно ампер-виткам тока опроса, и тем самым процесс восстановления разрядного сердечника ускоряется.

Величина источника смещения Е,м выбирается с таким расчетом, чтобы к моменту восстановления транзистор 2 перешел в закрытое состояние.

Таким образом, данный усилитель считывания позволяет уменьшить время восстановления разрядной части ПЗУ в несколько раз.

Формула изобретения

Усилитель считывания для постоянного запоминающего устройства, содержащий линейный дифференциальный каскад с нагрузочными резисторами на входе и источником смещения, подключенным в общую точку соедине4 ния резисторов, отличающийся тем, что, с целью повышения быстродействия, усилитель содержит элемент обратной связи, выполненный на транзисторе, база которого сое5 динена с источником смещения, коллектор подключен к одному из входов линейного дифференциального каскада, выход которого соединен через резистор с эмиттером транзистораа.

10 Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ № 2032630, кл, 21а 18/08, опубл. 1971.

2. Патент США № 3566296, кл. 380-30, 15 опубл. 1971.

3. Патент США № 3519850, кл. 307-235, опубл. 1970.