Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ц 58856l

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 22.04.74 (21) 2020551/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 15 01.78. Бюллетень № 2 (45) Дата опубликования описания 08.02.78 (51) М. Кл.2 G 11С 15/00

Государственный комитет

Совета Министров СССР

An делам изобретений и открытий (53) УДQ 681.327.6 (088.8) (72) Авторы изобретения

Г. В. Виталиев, A. Д. Гвинепадзе и Р. В, Смирнов (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

Изобретение касается запоминающих устройств.

Известно ассоциативное запоминающее устройство, содержащее адресные запоминающие блоки, разрядные шины которых соединены со входами соответствующих детекторов и через элементы ИЛИ первой группы— со входами выходного регистра, а адресные шины — с выходами соответствующих дешифраторов опроса, элементы ИЛИ второй группы, входы которых подключены к выходам регистров опроса и маски, а выходы — ко входам дешифраторов опроса, регистр операнда, информационные выходы которого соединены с одними входами элементов И, другие входы которых подключены к соответствующим выходам дешифратора операций, а выходы — ко входам регистров опроса.

В известном устройстве арифметические операции реализуются с помощью операций логического умножения, сложения по модулю два и сдвига, что существенно снижает его быстродействие.

Цель изобретения — повышение быстродействия при выполнении арифметических операций.

Эта цель достигается включением в состав устройства кольцевых сдвиговых регистров по числу дешифраторов опроса, выходы которых соединены с соответствующими адресными шинами запоминающих блоков, информационные входы подключены к выходам соответствующих дешифраторов опроса, а управляющие входы связаны с соответствующими управляющими выходами регистра операнда.

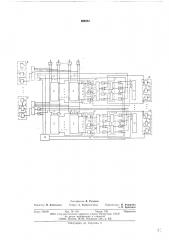

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит детекторы 1, адресные запоминающие блоки 2, разрядные шины 3 которых соединены со входами соответствующих детекторов 1, а через элементы 4 ИЛИ первой группы подключены к соответствующим входам выходного регистра 5. Регистр 5 выполнен на триггерах, организованных в ви15 де нескольких регистров сдвига. Адресные шины б блоков 2 соединены с выходами соответствующих дешифраторов опроса 7. Кроме того, устройство содержит элементы 8 ИЛИ второй группы, которые включены между вхо20 дами дешифраторов опроса 7 и соответствующими группами выходов регистра 9 опроса и регистра 10 маски, выполненных на триггерах.

Устройство также содержит регистр 11 опе25 ранда, разделенный на несколько регистров, «единичные» выходы 12 и «нулевые» выходы

13 которых подсоединены к соответствующим входам элементов ИЛИ 4 и регистра 9 через элементы И 14. Вторые входы элементов И 14

30 присоединены к соответствующим выходам

588561

25 зо

55 дешифратора 15 операций. В качестве элементов связи блоков 2 и дешифраторов 7 используются кольцевые сдвиговые регистры 16 на триггерах, выходы которых соединены с соответствующими шинами 6 блоков 2. Информационные входы 17 регистров 16 подключены к выходам соответствующих дешифраторов 7, а управляющие входы 18 связаны с соответствующими управляющими выходами 19 регистров 11. Регистр 10 разделен на несколько кольцевых сдвиговых регистров.

Работа устройства поясняется примером реализации операции сложения. Например, необходимо сложить два двоичных числа—

011 и 101. Первое из этих чисел хранится в одном из блоков 2 в виде кода 0000100, который записан в запоминающих элементах, соединенных с одной из шин 3 этого блока, т. е. на пересечении соответствующей разрядной линии и адресной линии с номером 011 хранится код «1», а в остальных элементах этой линии хранится код «О». Второе число заносится в регистр 11. В регистр 9 заносится код

111, например с выходов 12 и 13 регистра 11 через соответствующие элементы И 14, управляемые от дешифратора 15. На регистр 10 заносится код маски 110. Сигналы с выходов регистров 9 и 10 через элементы 8 ИЛИ поступают на вход дешифратора 7, что приводит к возбуждению 111, 101, 011, 001 выходов дешифратора 7. Код 10101010 с выходов дешифратора 7 передается на регистр 16 и циклически сдвигается на пять позиций при подаче пяти импульсов с выхода 19 регистра 11 (регистр 11 в этом случае работает в режиме счетчика) на входы 18 регистров 16. На шине

3 блока 2, в котором хранится первое слагаемое 00001000, появляется сигнал «О» (первый разряд суммы), который через элемент ИЛИ

4 передается на регистр 5 (при условии, если четыре сигнала «О» воспринимаются детектором 1 как «нулевой» сигнал). Далее код на регистре 10 циклически сдвигается, на выходе дешифратора появляется код 11001100, который также сдвигается регистром 16 на пять позиций, и на выбранной шине 3 появляется сигнал «О» (второй разряд суммы). В третьем такте код на регистре 10 еще раз циклически сдвигается, на выходе дешифратора появляется код 11110000, этот код сдвигается регистром 16 на пять позиций, а на выбранной шине 3 появляется сигнал «О» (третий разряд суммы). За три такта обращения к устройству происходит сложение двух трехразрядных чисел. Числа оольшей разрядности разбиваются на группы по несколько разрядов в соответствии с конфигурацией (числом адресных шин) блоков 2 (в данном примере на группы по три разряда). Переносы между группами определяются с помощью следующей процедуры. В триггера регистров 16 с номерами больше кода на регистр 11 (в данном примере 111, 110, 101, 100) заносится код «1», в соответствии с этим кодом возбуждаются шины 6 блоков 2 и на выбранной шине 3 появляется сигнал переноса (в данном примере

«О»), т. е. перенос в данной группе отсутствует, Сигнал переноса с шины 3 через элемент ИЛИ 4 поступает на регистр 5, с выхода которого он передается на счетный вход регистра 11 следующей (более старшей) группы.

Операция вычитания может быть реализована как операция сложения при замене второго слагаемого его дополнительным кодом.

Умножение и деление также реализуются заменой их последовательными сложениями и вычитаниями.

Описанное устройство наиболее эффективно для запоминающих блоков с непосредственной выборкой (выборкой по системе 2Д).

Формула изобретения

Ассоциативное запоминающее устройство, содержащее адресные запоминающие блоки, разрядные шины которых соединены со входами соответствующих детекторов и через элементы ИЛИ первой группы — со входами выходного регистра, а адресные шины — с выходами соответствующих дешифраторов опроса, элементы ИЛИ второй группы, входы которых подключены к выходам регистров опроса и маски, а выходы — ко входам дешифраторов опроса, регистр операнда, информационные выходы которого соединены с одними входами элементов И, другие входы которых подключены к соответствующим выходам дешифратора операций, а выходы — ко входам регистров опроса, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия при выполнении арифметических операций, оно содержит кольцевые сдвиговые регистры,по числу дешифраторов опроса, выходы которых соединены с соответствующими адресными шинами запоминающих блоков, информационные входы — с выходами дешифраторов опроса, а управляющие входы — с соответствующими управляющими выходами регистра операндаа.

588561

1, J °

Составитель В. Рудаков

Тсхрсд A. Камышннкова

Корректоры: Н. Федорова и Л. Брахнина

Редактор H. Каменская

Заказ 3264/6 Изд. № 159 Тираж 738 Подписное

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, %-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2