Фазосмещающее устройство асинхронного типа для управления вентильным преобразователем

Иллюстрации

Показать всеРеферат

(ii! 588612

Союз Советских

Соаависти-.вских

Респу1лик

g ЦТ<РР(: ДРА4У СОИДЕТСЛЬСЫУ (61) Дополнительное к авт. свид-ву (22) Заявлено 26.04.74 (21) 2019190/24-07 с присоединением заявки _#_o (23) Приоритет (43) Опубликовано 15.01.78. Бюллетень Мю 2 (45) Дата опубликования описания 06.02.78 (51) М. Кл.з Н 02Р 13/16

Государственнь и квинтет

Совета Мнннстров СССР оо делам изобретений и открытий (53) „"Д1(621 314.5 (088.8) (72) Авторы изобретения

В. А. Барский и С. В. Петров (71) Заявитель (54) ФАЗОСМЕЩАЮЩЕЕ УСТРОЙСТВО АСИНХРОННОГО

ТИПА ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ

ПРЕОБРАЗОВАТЕЛЕМ

Изобретение относится к устройствам управления вентильными преобразователями.

Известно фазосмещающее устройство асинхронного типа, содержащее входную цепь, интегратор на операционном усилителе, цепь обратной связи которого содержит параллельно соединенные конденсатор и ключ сброса, компаратор (нуль-орган) и логическое устройство. В момент выработки каждого импульса конденсатор цепи обратной связи интегратора разряжается через ключ сброса, управление которым производится сигналами с логического устройства. Погрешность отработки сигналов задания определяется временем разряда этого конденсатора через ключ.

Целью изобретения является уменьшение погрешности отработки сигналов задания. В описываемом устройстве это достигается тем, что в нем параллельно конденсатору цепи обратной связи интегратора и его ключу обнуления подключен конденсатор такой же емкости со своим ключом обнуления, входы обеих цепей обратной связи соединены с выходом операционного усилителя через ключи отключения.

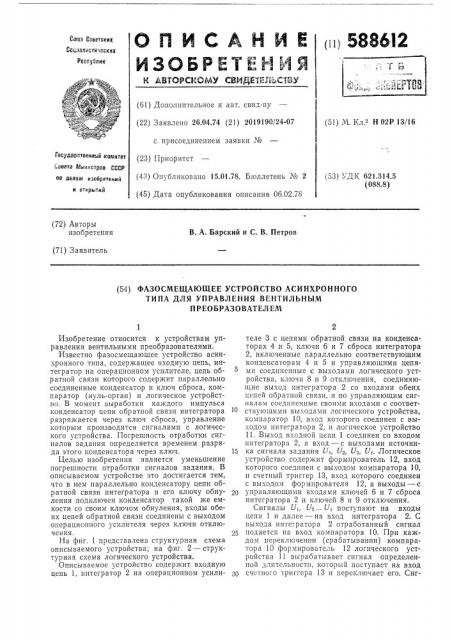

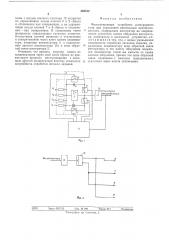

На фиг. 1 представлена структурная схема описываемого устройства; на фиг. 2 — структурная схема логического устройства.

Описываемое устройство содержит входную цепь 1, интегратор 2 на операционном усилителе 3 с цепями обратной связи на конденсаторах 4 и 5, ключи 6 и 7 сброса интегратора

2, включенные параллельно соответствующим конденсаторам 4 и 5 и управляющими цепями соединенные с выходами логического устройства, ключи 8 и 9 отключения, соединяющие выход интегратора 2 со входами обеих цепей обратной связи, и по управляющим сигналам соединенные своими входами с соответствующими выходамп логического устройства, компаратор 10, вход которого соединен с выходом интегратора 2, и логическое устройство

11. Выход входной цепи 1 соединен со входом интегратора 2, а вход — с выходами источни15 ка сигнала задания Пь U2, U, U;. Логическое устройство содержит формирователь 12, вход которого соединен с выходом компаратора 10, и счетный триггер 13, вход которого соединен с выходом формпрователя 12, а выходы — с управляющими входами ключей 6 и 7 сброса интегратора 2 и ключей 8 и 9 отключения.

Сигналы U>, Уа ... U, поступают на входы цепи 1 и далее — на вход интегратора 2. С выхода интегратора 2 отработанный сигнал подается па вход компаратора 10. При каждом переключении (срабатывании) компаратора 10 формирователь 12 логического устройства 11 вырабатывает сигнал определенной длительности, который поступает на вход зо счетного триггера 13 и переключает его. Сиг588612 ме еления

@42. 1

Ю га аар и ра

Заказ 3327/13

Изд. № 200

Тираж 917

НПО

Подписное

Типография, пр. Сапунова, 2 налы с входов счетного триггера 13 подаются на управляющие входы ключей б и 9 сброса и отключения как отпирающие, а на управляющие входы ключей 7 и 8 сброса и отключения — как запирающие. В следующем такте полярность управляющих сигналов меняется.

Коммутация ключей приводит к отключению и закорачиванию через ключ одного конденсатора, например конденсатора 4, и подключению другого конденсатора (5) к цепи обратной связи интегратора 2.

Очевидно, что процесс разряда одного из конденсаторов через свой ключ сброса не препятствует процессу интегрирования с помощью другого конденсатора поэтому снижается погрешность отработки сигнала задания.

Формула изобретения

Фазосмещающее устройство асинхронного типа для управления вентильным преобразователем, содержащее интегратор на операционном усилителе, ключи обнуления интегратора, компаратор и логическое устройство, отл и ч а ю щ е е с я тем, что, с целью уменьшения погрешности отработки сигналов задания, параллельно конденсатору цепи обратной связи интегратора и его ключу обнуления подключен конденсатор такой же емкости со своим ключом обнуления, причем эти цепи обратной связи соединены с выходом операционного

1о УсилителЯ чеРез ключи отключениЯ.