Устройство для деления двоичных чисел

Иллюстрации

Показать всеРеферат

О П И С А Н -N - Е"

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (11) 5896l1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт. саид-ву (22) Заявлено 050874(21) 2048599/18-24

2 (51) М. Кл, G 06 F 7/39 с присоединением заявки № (23) Приоритет

Говудоротвоккый комитет

Совета Мокоотрео СССР

Ао доком квооротооко о открытой (53) УДК681. 327 (088.8) (43) Опубликовано 25.01.78.Бтоллетень № 3 (45) Дата опубликования описания 150178 (72) %вторы изобретения

В.Ф. Ковалев и Т.С. Панова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение предназначено для выполнения операции деления и может найти широкое применение в цифровых вычислительных машинах.

Известно устройство для деления двоичных чисел, содержащее регистр частного, регистр делителя и сумматор (1) .

В таких устройствах за каждый цикл определяется одна цифра част- 10 ного и запись последней производится в первый разряд регистра частного.

Наиболее близким к изобретению техническим решением является устройство для деления двоичных чисел, 15 содержащее регистр делителя, регистр частного, блок анализа знаков, сумматор, блок выработки корректирующей единицы, блоки передачи кодов, два элемента И, два элемента ИЛИ, при- ЯО чем группы выходов блока анализа знаков подключены к входам соответствующих элементов ИЛИ, выходы которых подключены к первым входам соответствующих элементов И, к вторым входам 25 которых подключена шина управления устройства, выходы элементов H подключены к первым входам соответствующих блоков передачи кодов, вторые входы которых подключены к соответствую- ЗО

2 щим выходам регистра делителя, выходы блоков передачвь кодов подключены к соответствующим входам сумматора (2) .

В этом устройстве завтнсь единицы частного производится в первый разряд.

После окончания (ll -1) циклов, в каждом нз которых определяется одна цифра частного, необходимо потратить еще один цикл на сдвиг информации в регистре частного на один разряд влево.

И только тогда в младший разряд возможна запись корректирующей единицы.

Цель изобретения — повышение быстродействия устройства.

Достигается это тем, что выход первого элемента ИЛИ подключен к входу второго младшего разряда регистра частного, выход блока выработки корректирующей единицы подключен к входу первого младшего разряда регистра частного

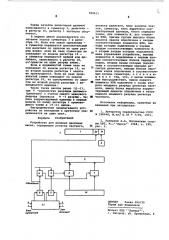

На чертеже приведено устройство для деления двоичных чисел без восстановления остатка.

Устройство содержит регистр 1 частного, блок 2 выработки корректирующе. единицы, сумматор 3, два элемента

И 4, 5, блоки 6 и 7 передачи ко ов, два элемента ИЛИ 8, 9, регистр 10 делителя, блок 11 анализа знаков.

589611

Знак сунна Ра афазию

Перед началом вычисления делимое записывается в сумматор 3, делитель— в регистр 10, регистр 1 частного обнуляется.

В первом цикле анализируется сочетание знаков сумматора 3 и регистра 10. Если эти знаки одинаковы— в сумматор передается дополнительный код делителя со сдвигом на один разряд влево если же знак сумматора не совпадает со знаком регистра 10— в сувщатор передается прямой код делителя, записанного в регистр 10, со сдвигом на один разряд влево.

Если в продвинутой сумке знак не совпадает со знаком регистра 10, то во второй разряд регистра 1 запись не производится. Если же знак продвинутой суммы совпадает со знаком регистра 10, то одновременно со сдвигом во второй разряд регистра 1 записывается единица. =

Число таких циклов passe ()) -1) где П -количество разрядов делимого (делителя) с учетом одного зиакоаого разряда (мантисса П «1 разряд) ° За- 95 пись корректирующей единицы в первый разряд по входу регистра 1 производится также в (.П -. 1) цикле.

Быстродействие предлагаемого уст» ройства по отношению к прототипу уве- 30 личивается на один цикл..

Формула изобретения

Устройство для деления двоичных чисел, содержащее регистр частного, регистр делителя, блок анализа знаков, сумматор, блок выработки корректирующей единицы, блоки передачи кодов, два элемента И, два элемента ИЛИ, причем группы выходов блока анализа знаков подключены к входам соответствующих элементов ИЛИ, выходы которых подключены к первые входам соответствующих элементов И, к вторым входам которых подключена шина управления устройства, выходы элементов И подключены к первым вхо« дам соответствующих блоков передачи кодов, вторые входы которых подключены к соответствующим выходам регистра делителя, выходы блоков передачи кодов подключены к соответствующим входам сумматора, о т л и ч а ющ е е с я тем, что, с целью повьзпения быстродействия, выход первого элемента ИЛИ подключен к входу второго младшего разряда регистра частного, выход блока выработки корректирующей единицы подключены к входу первого млацшего разряда регистра частного.

Источники информации, принятые во внимание при экспертизе:

1. Авторско свидетельство СССР

М 398948, М.кл, Ц 06,F 7/39 1971.

2. Папернов A.A ° Логические основы ЦВТ, М,, Наука 1968, с. 235 рис. 3.

ЦНИИПИ Заказ 393/35

Тираж 826 Подписное

Филиал ППП Патент, r Ужгород, ул. Проектная, 4