Регистр

Иллюстрации

Показать всеРеферат

С А Н И Е, „овеем, ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

® (61) Дополнительное к авт, свид-ву (22) Заявлено05.04.74 {2I f014671/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.01.78. Бюллетень № 3 (51) М. Кл. 6 11 С 19/00

Государственный нометет

Совета Мнннстров СССР оо делом нэаоретеннй н отнртетнй (533 У,ЦК681.327..66 (088.8) (45) Дата опубликования описания 25.01.78 (72) Авторы изобретении

Ю. 3. Воробьев и В. А. Грехнев (71) Заявитель (54) РЕГИСТР

Изобретение относится к области вычислительной техники и может быть использовано для хранения информации.

Известен регистр, выполненный на элементах И--HE, каждый разряд которого содержит триггер с раздельными входами и элемент

И -HE, причем выход этого элемента соединен с единичным входом триггера, а нулевые выходы всех триггеров регистра соединены с входами первого дополнительного элемента

И вЂ” НЕ, выход которого соединен с входом второго дополнительного элемента И†kIE, выход второго дополнительного элемента И вЂ” НЕ соединен с входами элементов И вЂ” НЕ всех разрядов регистра.

Однако устройство отличается низкой надежностью, вследствие разброса времени переключения реальных логических элементов. Действительно, при записи информации в регистр возможно, что какой-то триггер установится в состояние «единица» раньше, чем остальные триггеры, и через цепь обратной связи заблокирует весь регистр. Вследствие этого часть триггеров не успеет установиться в состояние

«единица» и информация в регистре окажется неверной.

Целью изобретения является повыаение надежности устройства.

Достигается это тем, что выход элемента

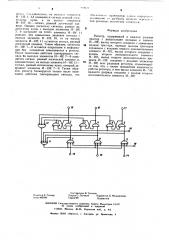

И--НЕ каждого разряда соединен е входом второго дополнительного элемента И вЂ” -1-IE, На чертеже дана схема регистра на три разряда.

Элементы И вЂ” НŠ— 6 попарно образуют триггеры в первом, втором и "третьем разряде регистра; 7, 8 и 9 — элементы И.— НЕ этих разрядов, первый дополнительный элемент

И вЂ” НЕ О, второй дополнительный элемент !

О И вЂ” -НЕ 11, информационные входы 12 — 14, выходы 15 — 17; шина 18 сигнала начальной установки регистра; шина !9 тактовых импульсов.

Схема работает следующим образом. В исходном состоянии все триггеры регистра нахо1 дятся в состоянии «Нуль», тактирующий сигнал, подаваемый на шину 19, равен логическому нулю. На выходах элементов И вЂ” НГ !, 3, 5, 7, 8, 9 — логическая единица, следовательно, на выходе И†HE IO — логический нуль, а на выходе И†HE ll — логическая единица, Предположим на входы 12 — 14 поступила информация III. С приходом тактирующего сигнала, равного логической единице, на выход элеМентов И вЂ” HE 7 — 9 появляются сигналы, равные логическому нулю, которые устанавлнвак>т триггеры всех трех разрядов в состояние «едиФормула uaoop(. re„us

Составнтель В. Грехнев

Техред О. Луговая Корректор Д. Мельниченко

Тнражт(7 Подписное

Редактор F.. Гончар

:так аз 463/49

ЦИИИПИ Государственного коннтета Совета Мнннстров СССР по делам изобретений н открытнй

1! 3035, Москва, Ж-35, Раушскан наб., д, 4/5

Фнинаи ППП <Патента, г. Ужгород, уи. Проектная, 4 ни1111:>. (.с(е/(овательно, Hd выходах элемеtlòott

И- llE I, 3,5 появляется сигнал, равный .:1(и.ическому нулю, а иа выход(элементов

И вЂ” -!!Е !0 — сигнал, равный логической единице. Однако поскольку сигналы, равные логи(ескому нулю, с выходов элементов И вЂ” llE

7---9 поступают на вход(элемента И вЂ” НЕ I! рань(пе, чем измененное значение сигнала с выхода элемента И--HE lO, то на выходе элемента И--НЕ !! (гстанется сигнал, равный логической единице. Таким образом, элементы

И--!-!Е 7 — 9 остаются открытыми и информация без искажения записывается в регистр.

После окончания действия тактирующего сигнала йа выходах элементов И вЂ” НЕ 7 — 9 появляется сигнал, равный логической единице, и, следовательно, на выходе элемента И вЂ” HE !— сигнал, равный логическому нулю, который закрывает элементы И вЂ” НЕ ? — 9. Таким образом, регистр блокируется только после окончания действия тактирующего сигнала, что Ф(C11(ъ 1И Н 1С I 1! Р((ВИЛЬНХ К1 4 <1 И И, Ь И! 1!1Р1! " 1;11 т,, l1e3нВис11мО o l j)n t6poca ((рсмсни (!(!1" к.тr. :( иия реальных Jt()(è÷åñêèõ элем! ltlo8, Регистр, содержащий в каждом разряде триггер с раздельными входами и элемент

И вЂ” НЕ, выход которого соединен с единичным входом триггера, нулевые выходы триггеров соединены с входами первого дополнительного элемента И вЂ” HE, выход которого соединен с входов. второго дополнительного элемента

И вЂ” -НЕ, выход второго дополнительного элемента И вЂ” -HE соединен с входами элементов

И†HE всех разрядов регистра, отличшощиася тем, что, с целью повышения надежности работы регистра, в нем выход элемента И вЂ” - . Е каждого разряда соединен с входом второго дополнительного элемента И вЂ” НЕ.