Резервированное оперативное запоминащее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

И3ОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДВТВДЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 08.10.75 (21)2180915/18-2 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 25.01. 78,Бюллетень №3 (45) Дата опубликования описания1о-о1 тЬ (" веоваз (51) M. Кл. б 11 С 29/00

Государственный комитет

Совета Министров СССР по делам иэооретений и открытий (53) У Д К 6 8 1. 327 (088.8.) (72) Авторы К. К. Е шин, В. И. 3 ар овский, A. М. С олда тов, А. И. К рив он ос ов изобретения,о,. Н. Мерзляков, В. Г. Деревянченко и Л. А. Городилова (71) Заявитель (54) РЕЗЕРВИРОВАННОЕ ОПЕРАТИВНОЕ

ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Известно резервированное запоминающее устройство, содержащее идентичные запоминающие блоки, блок коррекции и блок управления (1) .

Наиболее близким к изобретению техническим решением является резервированное оперативное запоминающее устройство, содержащее накопители, блок управления, подключенный к блокам свертки по модулю два, блоку поразрядного сравнения и коммутатору (2) .

Однако ограниченная корректируюшая способность этих устройств не позволяет исправлять в группе ошибки, кратность которых превышает единицу, что значительно снижает надежность устройства.

Целью изобретения является повышение на- 15 дежности устройства.

Достигается это тем, что устройство содержит входные и выходные коммутаторы, управляющие входы которых подключены к выходам блока управления, информационные входы входных коммутаторов соединены соответственно с входами устройства и выходом коммутатора,. а выходы — с входами соответствующих накопителей, входы выходных коммутаторов подключены соответственно к выходам накопителей, а выходы — к входам соответствующих gq

2 блоков свертки по модулю два и входам блока поразрядного сравнения и коммутатора.

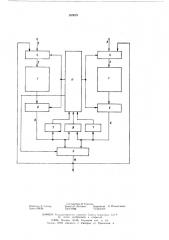

На чертеже изображена блок-схема резервированного оперативного запоминающего устройства, содержащего, например, два накопителя.

Устройство содержит накопители 1 (соответствующие разряды которых используются для хранения контрольной информации), входы 2 накопителей, а также входы 3 устройства соединены соответственно с выходами и одними информационными входами входных коммутаторов 4. Выходы 5 выходных коммутаторов 6 подключены соответственно к входам блоков 7 свертки по модулю два, блока 8 поразрядного сравнения и коммутатора 9, выход 10 которого соединен с другими информационными входами коммутаторов 4. Выходы накопителей 1 подключены к входам коммутаторов 6. Управляющие входы коммутаторов 4, 6 подключены к выходам блока управления 11, входы которого соединены с выходами блоков 7 и 8.

Устройство работает следующим образом.

Записываемая информация подается на входы 3 коммутаторов 4 в виде информационных слов с контрольными разрядами, например, для проверки на четность в каждом из них. В исходном состоянии входы 3 через входные

589623 коммутаторы 4 подключены к соответствующим входам накопителей 1. Лналогично выходы накопителя 1 через выходные коммутаторы 6 подключены к выходам 5 этих коммутаторов.

При считывании сигналы информационных слов проходят на блоки 7 свертки и блок 8 поразрядного сравнения. Если соответственный блок свертки не обнаруживает ошибки в считанном слове, то на его выходе вырабатывается информация об отсутствии ошибки и блок 11 выдает сигнал коммутатору 9 на пропуск на выход 10 информации из соответствующего накопителя 1.

При возникновении в первом накопителе 1 (левый на чертеже) одиночной ошибки блок управления 11 разрешает пропуск на выход 10 информационного слова с второго накопителя 1. При устойчивом повторении ошибки при считывании информации в одном н том же разряде из накопителей блок 11 запоминает номер отказавшего накопителя и номер отказавшего разряда. Номер отказавшего накопителя определяется при помощи блоков свертки 7, номер отказавшего разряда — при помощи блока 8 поразрядного сравнения. Блок 11 вырабатывает сигнал о переключении по которому соответствующий коммутатор 4 подключает входную шину отказавшего оазряда к входнои шине контрольного разряда соответствующего накопителя 1. По этому же сигналу выходной коммутатор 6 неисправного накопителя 1 подключает шину контрольного разряда к выходной шине неисправного разряда. После переключения блок 11 осуществляет перезапись всей информации из исправного накопителя 1 в неисправный. В процессе перезаписи информация неисправного разряда записывается в разряд, где ранее хранилась контрольная информация. Одновременно отключается соответствующий блок свертки 7. В результате перезаписи в этом накопителе восстанавливается вся информация за исключением контрольного пазряда.

Если в процессе дальнейшей работы блок 8 опять обнаружит несовпадение разрядов в информационных словах, поступающих с обоих накопителей (произойдет еще один отказ), то сигнал от блока свертки 7, связанный с вторым накопителем 1 там, где этот блок не был отключен, покажет, есть ли искажение информации во втором накопителе 1. Если такое искажение есть, то считается, что в первом накопителе 1 информация не искажена и блок 11 через выходной коммутатор 6 пропускает эту информацию на выход 10 коммутатора 9. Если блок свертки 7 не отмечает искажения, то считается неискаженной информация второго накопителя, которая и передается на выход 10 коммутатора 9.

Таким образом, описанное устройство позволяет при простом потоке отказов исправлять две ошибки. При использовании не двух, а большего числа (Р) накопителей в таком устройстве исправляется 2(Р— 1) ошибки, что в два раза превышает кратность ошибок, исправляемых в обычных P-канальных устройствах с контролем в каждом канале.

Формула изобретения

Резервированное оперативное запоминающее устройство. содержащее накопители блок управления, подключенный к блокам свертки

2s по модулю два, блоку поразрядного сравнения и коммутатору, отличающееся тем> что, с целью повышения надежности устройства, оно содержит входные и выходные коммутаторы, управляющие входы которых подключены к выходам блока управления информационные входы входных коммутаторов соединены соответственно с входами устройства и выходом коммутатора, а выходы — с входами соответствующих накопителей входы выходных коммутаторов подключены соответственно к выходам нако35 пителей а выходы — к входам соответствующих блоков свертки по модулю два и входам блока поразрядного сравнения и коммутатора.

Источники информации, принятые во внимание при экспертизе:

1. Лвторское свидетельство СССР ¹ 439020, 4о кл. G 11 С 29i00, 1972.

2. Патент СШЛ № 3685015. кл. 340 — 141.1, 1972.

589623

Состьмигель В. Рудаков

Техрел О. Луговая Корректор Л Мельниненко

Тирзж7! б Подписное

Редактор Е. Гончар

Вака : 396/36

ЦНИИ!1И Рос)да; стаенного когиитета Сове;а 31инистрс в СССР по делана изо6ретеннй и откры1ий

I 13035, Москва,:К-35, Раугнскаа най., д. 4/5

:Ъил!aë I11111 «11атент», г. Ужгород, ул. Проектная, 4