Устройство приоритетного обращения к памяти цифровой вычислительной машины (цвм)

Иллюстрации

Показать всеРеферат

59074!

Союз Советских.Социалистических, Республик

1.Кл G 06 F 9)18

Государственный комитет

Совета Министров СССР по делам изобретений и открытий, УДК 681.325 (088.8) (72) Авторы изобретения

Н. М, Абакумова, А. М. Вербовский, Н. С. Зеленский, А. Г. Кухарчук, А. Д. Мороз и Л. A. Струтинский

Ордена Ленина институт кибернетики Академии наук УССР (71) Заявитель (54) УСТРОЙСТВО

ПРИОРИТЕТНОГО ОБРАЩЕНИЯ

К ПАМЯТИ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ

Изобретение относится,к области вычислительной техники, в частности, к устройствам приоритета и может быть использо|вано при построении вычислительных машин и систем.

Извес но приоритетное устройство (1), содержащее для определения приоритетности при обращении к отдельным блокам, памяти общее поле запросов, состоящее из отдельных приоритетных устройств, охваченных шинами разрешения доступа к каждому блоку памяти и шинами запросов разной степени срочности. Такое устройство может иметь только оди н коэффициент расслоения памяти и не может перестраиваться.

Известно также приоритетное устройство (2), включающее приоритетные схемы блоков оперативной памяти и логические схемы, содержащие триггеры хранения сигналов готовности блоков оперативной памяти и ждущий мульти ви братор формирования сигналов опроса триггеров хра нения. Это устройство позволяет определить приоритетность при выдаче сигналов готовности различным блокам памяти в один и тот же источник запросов при обращении к блокам оперативной памяти в цифровой вычислительной системе путем использования динамического приоритета. Его недостатком является невозможность менять режим расслоения памяти.

Наиболее близким к изобретению является устройство приоритетного обращения к памяти ЦВМ (3), содержащее блок анализа состоя ния запрашиваемых блоков памяти, первая группа входов и выходы которого соеди5 нены соответственно с первой группой управ;IIIIoIIIHx входов устройства и с первой группой входoB блока динамического хранения приоритетных запросов; блок анализа приоритетных запросов, входы и выходы которого соединены соответственно с выходами блока динамического хранения, приоритетных запросов и с первой группой входов блока выделения запросов адреса слова и номера блока памяти, причем вторая группа входов блока

15 динамического хранения приоритетных запросов, третья группа вхадов и выходы блока выделения запросов адреса и номера блока памяти соединены соответственно с группой запросных входов, со второй группой управляющих входов устройства и с выходами устройства, а тактовый вход блока динамического хранения приоритетных запросов — с тактовым входом устройства. Однако это уст,ройство имеет довольно узкие функциональ25 ные,возможности, так как не обеспечивает организацию переменных режимов расслоения .памяти ЦВМ.

Цель изобретения — расширение функциоH3;IbHbIx возможностей путем обеспечения пеЗO ременного режима расслоения памяти ЦВМ.

590741

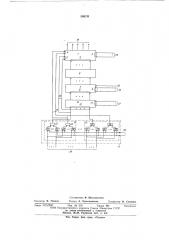

Поставленная цель достигается тем, что уст- 2, 1. Старший разряд адреса памяти (15-й)

poHcTIBo содержит многоканальный коммута- определяет номер блока, а младшие (1— тор, первая и вторая группы выходов и груп- 14) — адрес сло ва в блоке памяти. 1 и 15 па управляющих входов которого соединены разря ды поступают на вход коммутатора 18, соответственно с третьей и четвертой группа- 5 а 2 — 14 разряды на,входы группы 22. При ми входов блока выделения запросов адреса расслоении с коэффициентом 2 разряды адреслс ва и номера блока памяти и с третьей са комиутируются в ко ммутаторе 18 таким группой упра вляющих входов устройства, лри- образом, что 1 разряд определяет, номер блочем каждая группа адреаных входов комму- ка памяти, а 15 разряд становится разрядом татора соединена с соответствующей группой 10 адреса слова. В результате адрес слова опреадресных входов устройства, а каждый канал деляется разрядами 2 — 15. При наличии чекоммутатора содержит первый и второй эле- тырех блоков памяти адресная разрядная сетменты ИЛИ и первую и вторую группы эле- ка 1 — 16. При коэффициенте расслоения 4 ментов И, причем выходы первой группы эле- разряды 1 и 2 определяют, номер блока паMPH ToIB И канала соединены через rrepiBbIH 5 мяти, а 3 — 16 — адрес слова. При наличии элемент ИЛИ с соответствующим выходом шести блоков памяти а дреоная разрядная первой группы выходов коммутатора, выходы сетка 1 — 17, В этом случае коэффициент расвторой группы элементов И канала через вто- слоения может быть равным 2 или 0 (без рой элемент ИЛИ соединены с соответствую- расслоения); разряды 17, 16 и 1 — опреде щим выходом второй группы выходов комму- о ляют номер блока памяти, а 2 — 15 — Разрятатора, первые входы одноименных элементов ды адреса слова. Следовательно, rrpH е ет 1 первои и второи групп канала соединены лом количестве блоков памяти коэффициент с соответствующим входом группы управляю- расслоенич всегда ра вен 0 (без расслоения), щих входов коммутатора, вторые входы одно- при четном, но не равном 2 количестве 6»именных элементов И первой .и второй групп KoB коэффициент .расслоения может быть 0 и -го канала соединены с соответствующим 2 а если количество блоков памяти равно 2, входом -ой группы адресных входов устрой- то коэффицент расслоения может быть ства, вторая группа выходов:коммутатора 0 и 2 . соединена со второй группой входов блока При работе устройства в режиме без Расанализа состояния запрашиваемых блоков слоения разрешающий потенциал присутствует,на верхнем входе группы 28, а запрещаСтруктурная схема предлагаемого устрой- ющий — на остальных входах. В режиь е работы с коэффициентом расслоения 2 разревь деления запросов шающий потенциал,rrpHci тствует на втором дР слова и "омера блока памЯти с пеР- 55 сверху входе группы 28, а запрещающий— вой 2,вто ой8 т торой 8, третьей 4 и meTBep TOH 5 Ha trpyiTHz входах этой группами входов, блок б анализа приоритет- младшие разряды адреса с помощью элеменных запросов, блок 7 динамического хране- тов И 27 через элементы ИЛИ 2б коммyTHpy ния приоритетных запросов с первой 8 и вто- ются на группу 12 входов блока 10, а старш"е ж входов блок 10 анализа со 4О epea azeMeHTbr N 28 H элементы ИЛ стояния запрашиваемых блоков памяти с пер- ва груп ну 4 входов блока 1. второй 12 группами входов, много- В результате анализа состояния запрашиканальный коммутатор 18 с первой 14 и вто- ваемых блоков памяти, которые поступают ло р " руппами выхадов и с первым 1б и входам группы 21, блок 10 по соответствую и-ным 17 ка нала. 45 IIIHM BbrxopaM выд просных входов, тактовый вход 20, первую даются по входам группь 8 в 6 оК

pyro 22 и третью 28 группы управля- с абатывает при наличии запРосов лодавае ющих входов и грулпы 24 адресных .входов. мых по входам группы 19, к свободному бло

1д " канал коммутатора содержит эле- к памяти ЦВМ и пРи наличии синхРосигна

И 25 и 2б, элементы И 27, образу- 50 ла на тактовом входе 20 устройства. B блоке у ющие первую группу и элементы И 28, обра- g происходит выделение, наиболее приорите зующие вто ного из запросов, поступивших на его входы, П и об а енин р бращении к блокам памяти UBM на Влок 1 выделяет разряды адРеса слова более группы 24 вхо о руп входов поступают разряды адреса приоритетного устройства. При 3TQM Ha BbI па мяти: на левые входы — старшие разряды, 55 ходы 18 устройспва поступают р Р те " на правые р е входы — младшие. TIo входам сигналы,,разряды адреса í™ра 620Ка па -"я группы 19 поступают .запросы от различных ти и разряды адреса crroBa

При нечетном количестве блоков памяти пы 28 — л изнар готовности блоков памяти, а по входам груп- в ЦВМ устройство всегда будет работать без — признаки режима ра боты (режимы 5О расслоения. При четном количестве блоков памяти, но не равном 2", стройство может расслоения). расслоелия реализуются в устрой- работать без расслоения или с Расслоением

У стве след ю и,м о дующим образом. На пример, источ- только на два блока. Если количество блоков ник запросов имеет 15 разрядов адреса па- равно 2", устройство может работать без рас1, 10, 9, 8, 7, 6, 5, 4, 3, 55 слоения,и с расслоением на 2, 4 и т. д. бло590741 ков памяти. От величины, коэффициента pdcслоения зависит время ожидания при обращении к блокам памяти. Это дает условное уменьшение общего цикла обращения к бло,ку памяти. 5

Формула изобретения

Устройство приоритетного обращения к памяти цифровой вычислительной машины, 10 содержащее блок анализа состояния запрашиваемых блоков памяти, первая грулпа входов и,выходы которого соединены соответственно с пер вой группой управляющих входов устройства и с первой группой входов блока динамического хранения приоритетных запросов; блок анализа приоритетных запросов, входы и выходы которого соединены соответственно с выходами блока динамического хранения приоритетных запросов и с первой группой входов блока выделения запросов адреса слова и номера блока памяти, причем вторая группа входов блока динамического хранения приоритетных запросов, третья группа входов и выходы блока выделения за- 25 просов адреса и номера блока памяти соединены соответственно с группой запросных входов, со второй группой упра|вляющих входов устройства и с выходами устройства, а тактовый вход блока ди намического хране- ЗO ния приоритетных запросов с тактовым входом устройства, о т л и ч а ю щ ее с я тем, что, с ццеелльью ю рраассшшиирреенниия я ффууннккциональных возможностей путем обеспечения переменного режима расслоения памяти ЦВМ, устройство 55 содержит многоканалыный коммутатор, первая и вторая группы выходов и группа управляющих входов которого соединены соответственно с третьей и четвертой группами входс в блока выделения за просов адреса слова и номера блока памяти и с третьей группой управляющих входов устройства, причем каждая группа адресных входов коммутатора соединена с соответствующей группой адресных входов устройства, а каждый канал коммутатора содержит первый и .второй элементы ИЛИ и первую и вторую группы элементов И, причем выходы первой группы элементов И канала соединены через первый элемент ИЛИ с соответствующим выходом первой группы выходов коммутатора, выходы второй группы элементов И канала через,второй элемент ИЛИ соединены с соответствующим выходом второй группы выходов коммутатора, первые входы одноименных элементов И первой и второй групп канала соединены с соответствующим, входом группы управляющих входов коммутатора, вторые входы одноименных элементов И первой и второй групп i-го канала соединены с соответствующим входом i-ой группы адресных входов устройства, вторая группа выходов коммутатора соедине|на со:второй группой входов блока анализа состоя пня запрашиваемых блоков памяти.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 288417, кл. G 06 F 9/18, 1969.

2. Авторское свидетельство СССР № 281901, кл. G 06 F 9/18, 1969.

3. Авторское свидетельство СССР

¹ 458828 кл G 06 Р 9/18 1974

590741

Г

)

) )

I )

) )

) )

Составитель Ф. Шагиахметов

Техред А. Камышникова

Редактор Н. Громов

Корректор И. Симкина

Подписное

Заказ 1013/2067 Изд. № 210 Тираж 881

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-З5, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»