Устройство переменного приоритета

Иллюстрации

Показать всеРеферат

Са зео и, Q Д Я С Д Я g Я / <„>gglQQ+g и 3 О БР кте н и я, г-,: —,,Социалистических, Республик (оl) Ч,Кл 2 G 06 F 9/18

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.325 (088.8) (72) Авторы изобретения (71) Заявитель

В. П. Школин, В. И. Тужилин и С. Ф. Михайлов (54) УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство переменного приоритета (2), содержащее блок хранения ходов приоритетов, выходы которого соединены с кодовыми входами коммутатора, регистр запросов, разрядные выходы которого соединены с первыми входами соответствующих элементов И группы, причем выходы элементов

И группы соединены с соответствующими управляющими входами коммутатора, а разрядные входы регистра запросов соединены с запросными входами устройства, Изобретение относится к области вычислительной техники, в частности, к устройствам переменного приоритета и может быть использовано при построении вычислительных комплексов и систем обмена информацией, Известно устройство переменного приоритета (1), содержащее регистры, дешифраторы, схемы совпадения, схемы сборки, схемы сравнения, триггеры, счетчик пропущенных обращений в каждой позиции приоритета с дополнительными схемами сборки и схемами совпадения.

Недостатком устройства является необходимость больших затрат оборудования при его реализации.

Недостатком устройства является значительная сложность его построения.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что разрешающие выходы коммутатора соединены со вторыми входами соответствующих элементов И группы, оповещающий выход регистра запросов, первый, второй кодовые входы блока хранения кодов приоритетов и опросный вход коммутатора соединены соответственно с выходом и управляющими первым, вторым и третьим входами устройства, индикационные выходы которого соединены с

15 разрешающими выходами коммутатора, а коммутатор выполнен в виде матрицы, в которой первые входы элементов строки соедиHeHû с соответствующим кодовым входом коммутатора, опросный вход которого соеди20 нен со вторыми входами элементов столбца матрицы, первые выходы элементов столбца матрицы соединены со вторыми входами элементов предыдущего столбца матрицы, вторые выходы элементов строки матрицы соединены с соответствующим разрешающим выходом коммутатора, третьи входы элементов строки матрицы соединены с соответствующим управляющим входом коммутатора.

Поставленная цель достигается такжс тем, что элемент матрицы содержит деши590742

Этот сигнал поступает на один из входов элемента И 7З. Поскольку на другой вход этого элемента поступает нулевой сигнал с регистра 8 (третий аоонент нс посылал запроса), сигнал с выхода элемента И 7, поступает на входы элементов 5„, 5,2 5,, Разрешающий уровень имеется только на элементе И 16 элемента 5:, матрицы. Именно через этот элемент сигнал поступит на вторые входы элементов второго столбца матрицы (т. е. на элементы 512, 522, 5-.2).

Теперь сигнал появляется только на выходе элемента 512, т. к. разрешающий уровень присутствует только на выходе одного дешифратора всех элементов этого столбца, а именно, дешифратора 14 элемента 51, (псоl выи абонент, которому соответствует код с первого выхода блока 1, имеет оолее высокий приоритет, чем второй абонент) .

Сигнал с выхода элемента 5г2 не пройдет через элемент И 7-., т. к, на другом входе этого элемента присутствует запрещающий потенциал (есть запрос OT первого абонента).

По выходу 12 абоненту посылается сигнал, оповещающий або! сита о том, что его запрос может быть представлен и обсл7живлни!о.

Первый абонент снимает свой запрос, а по выходу 9 снова поступает сигнал на блок управления 18, сообщая о том, что в регистре

8 имеются другие необслуженные запросы (в данном случае, запрос от второго абонента).

Блок управления 18 вновь формирует сигнал опроса по входу 10, и работа устройства возобновляется аналогично описанному.

Изобретение позволяет упростить известное устройство за счет исключения блоковформирователей, регистра блокировки и ряда взаимосвязей.

1. Устройство переменного приоритета, содержащее блок хранения кодов, приоритетов, выходы которого соединены с кодовыми входами коммутатора, регистр запросов, разрядвые выходы которого соединены с первыми входами соответствующих элементов И группы, причем выходы элементов И группы соединены с соответствующими управляющими входами коммутатора, а разрядные входы регистра запросов соединены с запросными входами устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, разрешающие выходы коммутатора соединены со вторыми входами соответствующих элементов И группы, оповещающий выход регистра запросов, первый, второй кодовые входы блока хранения кодов приоритетов и опросный вход коммутатора соединены соответственно с выходом и управляющими первым, вторым и третьим входами устройства, индикационные выходы которого соединены с разрешающими выходами коммутатора, а коммутатор выполнен в виде матрицы, в которой первые входы элементов строки соединены с соответфратор и два элемента И, причем первыи, второй, третий входы и первый, второй выходы элеме1гга матрицы соединены соответственно со входом дешифр-тора, с1в -.. 11р ра, с первым входо"!

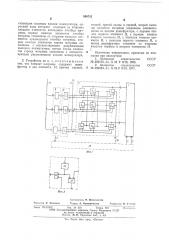

;:õ;0лэм первого элемента И, с первым . Торого элемента И, с выходом второго элемента И, с вь1ходом первого элемента И, а торыми выход дешифратора соединен со вто входами перво-о и ".-,Tîðîãî элементов И. ! стг.а, на фиг. 2 — структура элемента матP; I 1 j I i х! (!, г. ) . ок 1 .;ранения кодов приоритетов входы 2 8, " Р, коммутатор 4 с элементами

Г

I Ii 12r ° ° ° 17!; 2lr 222r

„„., группу 6 элементов И с элементами И 71, И 7„-,..., И 7-„, регистр 8, выход 9, входы 10, 11, выход 12. Позицией 18 обозначен блок управления.

Элемент матрицы содержит (фиг. 2) дешифратор 14, элементы И 15, 16.

Устройство

p " раоотает следующим образом.

Рассмотрим

Р, . для конкретности случай, кода п=З, т. е. к . оммутатор 4 содержит всего

9 элементов: 5;, 5 5 5, 5, 5„, 21, э22, зз, регистр 8 содержит 8 триггера, а г ипа 6 элемент а, а групИ72 И 7з . елтов И содержит элементы И 7

Ii

Г1усть код приоритета первого абонента равен двум д, второго — трем, третьего— единице, п иче. д, р м старшим по приоритету является третий абонент. Предположим, что по входу 11 нов х,, с пили запросы только от первого и вто г т рого абонентов, т. е. единичнь:е сигналы присутствуют только на входах элементов И 71 и И 7 .

Перед началом обмена произв п оизводится запись кодов приоритетов в блок 1 хранения а онента, для ду 2 поступают коды приоритекодов п ио тов, а по входу 8 — коды абонентов. 3 — в. апись ком п приоритетов может производитьс б управления 18 программным способом или с пульта оператора. В результате чего, на первые входы элементов 51 5 5 (. на е

11 12 1З (Т. Е.

: а дешифраторы 14) поступает код 2, при этом с выхода дешифратора 14 элемента 512 устанавливается разрешающ щии уровень для прохождения сигнала опроса со входа 10 ченалогично устарез элементы И 15, И 16. Аналоги навливаются разрешающие уровни на выходах дешифраторов 14 элементов 521 и 522.

Далее на вход 9 блока управления 18 поналичие ступает сигнал, указывающий на запросов в регистре 8. Блок управления 18 выдает на вход 10 устройства сигнал опроса.

Этот сигнал поступает на вторые входы элементов 51З, 52З и 5.-, коммутатора 4, т. е. на тервые входы элементов И 15 (фиг. 2)

Однако аз, р зрешающии уровень появится

;олько на выходе дешифратора 14 элемента 4з, и, следовательно, сигнал появится только на выходе элемента И 15 элемента 5З, матрицы.

Формула изобретения

590742! (Риг.

Раг.Г

Со"тавитель Ф Шамахметов

Техред А. Камышникова Корректор В. Гут:ан

Редактор Р. Киселева

По-,пнсноз

Заказ 1013/2067 Изд. ¹ 210 Тираж 881

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Тпп. Харьк. Фил. пред. «Патент» ствующим кодовым входом коммутатора, опросный вход которого соединен со вторыми входами элементов последнего столбца матрицы, первые выходы элементов столбца матрицы соединены со вторыми входами элементов предыдущего столбца матрицы, вторые выходы элементов строки матрицы соединены с соответствующим разрешающим выходом коммутатора, третьи входы элементов строки матрицы соединены с соответствующим управляющим входом коммутатора.

2. Устройство по п, 1, о тл и ч а ющ е ес я тем, что элемент матрицы содержит дешифратор и два элемента И, причем первый, второй, третий входы и первый, второй выходы элемента матрицы соединены соответственно со входом дешифратора, с первым входом первого элемента И, с первым входом второго элемента И, с выходом второго элемента И, с выходом первого элемента И, а выход дешифратора соединен со вторыми входами первого и второго элементов И.

10 Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 292155, кл. G 06 F9/18,,1969.

2, Авторское свидетельство СССР

¹ 359653, кл. G 06 F 9/18, 1971.