Цифровой фильтр

Иллюстрации

Показать всеРеферат

ОП ИСА НИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 25.07.75 (21) 2160002/18-24 с присоединением заявки ¹â€” (23) Пр иоритет— (43) Опубликовано 30.01.78. Бюллетень ¹ 4 (45) Дата опубликования описания 08.02.78 >59О749

Соаэ Советских

Социалистических.

Реслублик (51) М.Кл.- G 06 Г 15 32

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.325 (088.8) (72) Автор изобретения (71) Заявитель

10. А. Желнов (54) ЦИФРОВОЙ ФИЛЬТР

Предлагаемый цифровой фильтр относится к специализированным вычислительным устройствам и может использоваться в системах автоматического у правления или технике связи для фильтрации сигналов.

Известен цифровой фильтр (1), реализующий линейное разностное уравнение вида т fl

U, (К) =+à;Ь, (К вЂ” т) — Ь,UÄ (/I . — 1), (1)

1о J-O где Ul u Uq — соответственно входная и выходная последовательности фильтра;

У(— дискретное относительное время; а;а; — коэффициенты фильтра (постоянные величины).

Этот фильтр содержит регистры для хранения дискретных значений .входной и выходной последовательностей, множительные устройства, сумматоры, запоминающие устройства коэфф ициентов.

Из известных устройств, наиболее близким к предлагаемому техническому, решению является цифровой фильтр (2), содержащий

i(m+1) l-разрядных регистроз, запоминающее устройство и первый накапливающий сумматор, причем (т+1) l-разрядных регистров соединены последовательно и выходы каждого из них подключены к первой группе входов умножителя, вторая группа входов которого соединена с выходом запоминающего устройства, l старших разрядов выхода умножителя через первый на капливающий сум,матор подключены к,входу первого из последовательно соединеннь|х 1-разрядных регистров, выходы которых соединены с третьей груп пой входов умножителя.

Недостатком известного устройства является низкая точность.

Целью настоящего изобретения является уменьшение дисперсии результирующей ошибки округления, т. е. повышение точности цифрового фильтра.

Поставленная цель изобретения достигается тем, что в него введены n(y+v)-разрядных регистров и второй .накапливающий

20 сумматор, причем, (y+v) старших разрядов выхода умножителя соединены с входом второго накапливающего сумматора, а у младших разрядов выхода умножителя связаны с младшими разрядами входа второго накапливающего сумматора, v старших разрядов выхода которого связаны с v младшими разрядами первого накапливающего сумматора, а выход второго накапливающего сумматора соединен с входом первого из последователь30 но соединенных (y+ v) -разрядных регист590749 ров, подключенных своими выходами к четвертой группе входов х;множителя.

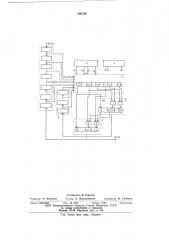

Функциональная схема предложенного устройства изображена,на чертеже.

Она содержит входную и,выходную по- 5 следовательности UI(K), U (K), ... UI„,+„I (К)

napaллельных t-разрядных регистров 1, (Р;О, P 1,...., Р 0„+,н), умножитель 2, первый накапливающий сумматор 8, запомиHBIoщее устройство 4, блок управления 5, второй накапливающий сумматор б, входные элементы ИЛИ 7, (y+v) -разрядные |параллельные регистры 8 (P 21 — Р n).

Вход цифрового фильтра подключен к цепочке (m+ 1) последовательно соединенных

l-разрядных параллельных регистров 1, выходы которых связаны с,первым входом умножителя 2. Второй вход умножителя связан со входом умножителя 4, l — старших разрядов (у+.l+v) -разрядного умножителя 20 подключены ко входу первого накапливающего, сумматора 8, а (у+ъ) младших разрядов умножителя — ко вход3 второго tHBKanливающего сумматора б. 1х младшим разрядам этого жс сумматора подключены у млад- 25 ших разрядов умножителя. Старшие разряды второго накапливающего сумматора подключены к старшим разрядам первого накапливающего сумматора,,выход которого связан с цепочкой последовательно соединенных разрядны.: регистров 1 (P20„+I) — Р,а„ч,о) подключенных своими выходами,ко входу ум,ножителя.

Выход второго накапливающего сумматора б связан с,входом цепочки последовательно вкл|оченных (y+v) -разрядных регистров 8, .выходы которых соединены с входом умножителя.

Выход блока управления УУ связан с управляющими цепями всех регистров, умножи- 40 геля, запоминающего блока и накапливающих сумматоров (для упрощения схемы эти связи на фиг. 1 не показаны).

Повышение точности в предлагаемом цифровом фильтре обеспечивается следующим 45 образом. Результирующая ошибка округления на выходе известного цифрового фильтра определяется соотношением:

m л

50, (К) =r, (K — i)+УЗ; (К вЂ” 1)—

i=-0

П 1 1- о (K )

j=I (2) 55 где в0 —,последовательность результирующих ошибок округления;

u;); — ошибки округления до l-го двоичного разряда при округлении в умножнтеле,произведений 0;UI (К вЂ” i), 60

IIIUI (К вЂ” i) соответственно.

В предлагаемом цифровом фильтре с помощью дополнительного контура обратной связи, содержащего накалливающий сумматор и регистры 8, формируегся сигнал в 0 (К), который суммируется с выходным сигналом фильтра и компенсирует ошибку е0(К).

Величина v, определяющая совместно с у разрядностью цепи дополнительной обратной связи, выбирается равной максимально возможному количеству двоичных разрядов, на которое может распространяться сшибка е0 т. е.!

v ==-1Og> (=ol „„,, где -ÿ 0,„,, — максимальное значение результирующей ошибки округления.

Такой выбор v ооеспечивает отсутствие переполнения разрядной сетки при вычислениях в контуре дополнительной обрат ной связи.

Величина 1 выбирается в зависимости от требуемой точности фильтра.

Формирование компенсируюшего сигнала, (К) производится путем последовательных вычислений по ура|внению (2) после окончания вычисления по соотношению (1) .

Одновременно с вычислениями по соотношению (1) с помощью накапливающего сумматора б нроизводится вычисление суммы ти 2 х; (11 — i ) + 2 3; (i — j). (4) 1=0

Величина а;, Р; .предста|зляет собой у младших разрядов l+y-разрядных произведений а; UI, b; Uq. Умножение,на 2 (сдвиг влево) 1величин а;, P. обеспечивается схемно путем соединения l+1, l+2,..., . (1+у)-го выходных разрядов умножителя соотвегственно с v+1, v+2,.... (y+v)-ым разрядами накапливающего сумматора б.

После накопления суммы (4) вычисляется величи.на

-"-; (К) = Q 2 —" 0,; (К вЂ” i) -, —

i — o

/1 (К вЂ” 1) — 2". bj 2 - -., (K — 1) + 2

j=1 (5) Значения 2 =-, (К вЂ” j), вычисленные на предыдущих шагах, хранятся на регистрах 8. Их умножение на коэффициенты производится последовательно в умножителе 2. Накопление суммы, стоящей в правой части равенства (5), производится сумматором б.

Бычисленныи по соотношению (5) сигнал сдвигается вправо на — (l — v) двоичных разрядов и суммируется с сигналом У (К) на накапливаюшем сумматоре 8. Сдвиг вправо (умножение на 2 — н ") обеспечивается соединением 1, 2,.....-го разрядов накапливающего сумматора б соогветст венно с l »+1, l — v+2,...., l-ым разрядами сумматора.

Компенсирующая величина в, отличается от в0 из-за погрешностей, с которыми при ее вычислении представляются значения а;, Р. и ошибок округления, сопровождающих,вычисление, произведений Ь, 2, (К вЂ” j) и сдвиг величин 2 — я „вправо, при котором сохраняются только l старших разрядов.

590749

D, — = D(I0

20

D,- « — 2 — I Dl, D.,+ — 2 - (— « — ) Dl (7) 55

СССР

Для оценки результирующей ошибки округления в предлагаемом цифровом фильтре используется направленным граф его структуры. Вычисление значений выходной последовательности цифрового фильтра производится с помощью операций умножения, запоминания значений сигналов в дискретные моменгы времени и суммирования.

Операции сдвига (запоми(на ния) сигналов на единицу дискретного .времени изображены утолщенными ребрами графа, около ветвей графа, обозначающих операцию умножения, записан соответствующий коэффициент.

В узлах графа, в которые входит более одной ветви, происходит суммирование сигналов. Ошибки округления представляют собой случай нь«е последовательности (дискретные белые шумы),,действующие как помехи в реорах — ум(ножителях графа.

Ошибки округления до l-го двоичного разряда изображены прямолинейными стрелками, ошибки округления до (l+y)-ro разряда — зигзагообразными стрел(ками, а ошибки округления до (у+ () -rо разряда — пунктирными стрелками.

Ошибки округления до (l+y)-го двоичного разряда сопровождают представление ошибок 2@у (l+y) -разрядными числами.

Ошибки округления до (l+y) двоичных разрядов связаны с конечной разрядностью накапливающего сумматора 5 и регистров 8.

Ошибка округления р, возникает при сдвиге вправо на (l — v) двоичных разрядов величины 2 †и сохранении при этом только 1 о старших разрядов.

Приведение ошибок округления до (1+V)го и (y+v)-го двоичных разрядов к выходу графа показывает, что дисперсия результирующей ошибки округления в в предлагаемом цифровом фильтре определяется, выражением

D, = (т+ и — 1) D(+«R -, -}- nD-,(»,, 2 — - ((— > R +В/, (6) где О(+.(D«+,, дисперсия ошиоок округления до (l+y)-го и (y+v)-ro двоичных разрядов.

Считая ошибки округления равномерно распределенными случайными величинами, можно показать, что дисперсии ошибок округления связа(ны соотношениями

С учетом соотношения (7) выражение для

D,- можно записать (в виде

D = (у((, -, — 2д + 1) 2-"D,R+ D(, (8) 25 зо

В оольшинстве практических случаев даже для небольших значений у — первым слагаемым в сумме (8) можно пренебречь, т. е.

Дисперсия результирующей ошибки округления в предлагаемом цифровом фильтре примерно равна дисперсии ошибки одного окуглвния до l-го двоичного разряда, т. е. ошибка при,вычислении выходной последовательности фильтра не,превышает одного— двух младших разрядов.

Таким образом, предлагаемый цифровой фильтр позволяет существенно уменьшить погрешности за счет ошибок округления и повышение точности фильтрации и тем самым существенно снизить стоимость систем обработки данных.

Формула изобретения

Цифровой фильтр, содержащий (m+n) lразрядных регистров, запоминающее устройство и первый (накапливающий сумматор, причем, (m+1) l-разрядных регистров соединены последовательно и выходы каждого из них подключены к первой группе входов умножителя,;вторая группа входов которого соединена с выходом запоминающего устройства, 1 старших разрядов выхода умножителя через первый накапливающий сумматор подключены к входу первого из и последовательно соединенных l-разрядных регистров, выходы которых соединены с третьей группой входов умножителя, отличающийся тем, что, с целью повышения точности, в него введены п(+ ()-разрядных регистров и второй накапливающий (сумматор, причем (y+ v) старших разрядов выхода умножптеля соединены с входом второго накапливающего сумматора, а у младших разрядов .выхода умножителя связаны с у младшимп разрядами входа второго накапливающего сумматора, старших разрядов выхода которого связаны с v младшими разрядами первого накапливающего сумматора, а выход второго накапливающего сумматора соединен с входом пер(вого из последовательно соединенных ($+ v) -разрядных регистров, подключенных своими выходами к четвертой группе входов .множителя.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство

¹ 463115, кл. G 06 F 7/38, 11.03.73, 2. Гольдберг Л. М. и др. Цифровые фильтры. М., Связь, 1974, стр. 116.

590749

Составитель В. Тарасов

Техред А. Камышникова

Корректор И. Сим кина

Редактор P. Киселева

Тип. Харьк. фил, пред. «Патент»

Заказ 1008/2066 Изд. № 208 Тираж 1109 Подписное

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5