Запоминающее устройство с автоматическим восстановлением работоспособности

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ р=оюз Сеаетских

Социалистических

Респубпик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (бв) Дополнительное к авт. саид-ву (22) Заявлено 18,10,76(21) 2412288 /18-24, (53) М. Кл.

G ll С 29/00 с нрисоединеннем заявки №вЂ” (23) Приоритет 090273 (согласно з-ке

1880596/18-24) (43) Оиублийовано 050278,Бтоллетень № 5

Гиирдарвтивииии иваитвт

Совета Мииивтрвв СССР ии ивиам ивобрвтвиий и открытий (53) У.ДК 628.327.6 (088. 8) (45) Дата оттублит(ования оинсания 1801.78 (72) Автор изобретения

А. К..Култьгин

Pl) Заявитель (54) ЗАПОМИНАтОЩЕе уСТРОЙСтВО С АВтОМАТИчеСкии ВОССТАНОЮ1ЕНИЕМ

РАБОТОСПОСОБНОСТИ (Изобретение относится к автоматике и .вычислительной технике, предназначено для использования в системах памяти.

Известны запоминающие устройства (3"), содержащие основные и резервные блоки, в которых при выходе из строя основного блока автоматически включается резервный (1).

Недостатком известных устройств является сложность схемы замещения отка- т0 завшего блока ЗУ резервным, для реализации их необходим значительный объем дополнительной аппаратуры, что сказывается на надежности ЗУ.

Наиболее близко .к предлагаемому 16 запоминающее устройство с автоматическим восстановлением работоспособности, содержащее блок выборки адресов, основные одноразрядные блоки памяти, шины записи и шины управления — по числу ЯО разрядов хранимой информации, резервный одноразрядный блок памяти; адресные входы основных и резервного одноразрядного блоков памяти подключены к выходам блока выборки адресов, соот т- 25 ветствующие шины записи соединены со входами Запись основных одноразрядных блоков памяти.

Недостатки этого устройства состоят в том, что в качестве входного и 30 выходного коммутаторов используются матричные переключатели, которые технологически сложны и требуют сложного управления; устройство содержит большое количество аппаратуры и сложно в изготовлении, матричные переключатели управляются с помощью реле, схема имеет низкое быстродействие.

Цель изобретения — упрощение и повышение быстродействия схемы.

Поставленная цель достигается тем, что в устройство введены инверторы, три группы элементов И и элементы ИЛИ.

Первые входы элементов И первой группы соединены с шинами записи соответствующих разрядов, вторые входы соединены с соответствующими шинами управления, со входами инверторов и с перными входами соответствующих элементон И второй группы, а выходы элементов И первой группы через элемент

ИЛИ соединены со входом Запись резервнсго одноразрядного блока памяти.

Вторые входы элементов И второй группы соединены с выходом резервного одноразрядного блока памяти, первые входы элементов И третьей группы соединены с выходами основных одноразрядных блоков памя — è, вторые нходы — с выходами иннерторов,а выходы соответ591966 и 2. В связи с отсутствием трансфор- маторных элементов и релейных,контактов быстродействие предлагаемого усройства может быть выше на несколько порядков. и4

Формула изобретения ствующих элементов И второй и третье групп соединены с соответствующими входами элементов ИЛИ.

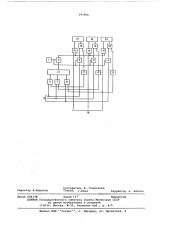

На чертеже представлена схема запоминающего устройства.

Выход блока выборки адресов 1 соед нен с адресными входами осйовных 2,3, «и резервйого 5 разрядных блоков памяти. Входы элементов И 6-8 соединены с соответствующими разрядами шин записи

9, которые соединены также с входами Запись блоков памяти 2-4, вторые входы элементов И 6-8 соединены с соответствующими шинами управления 10, со входами инверторов 11-13 и с первы ми входами элементов И 14-16. Выходы, элементов И 6-8 через элемент ИЛИ 17 соединены со входом Запись блока памяти 5, выход которого соединен со вторыми aõîäàìè элементов И 14-16.

Выходы блоков памяти 2-4 соединены с первыми входами соответствующих элементов И 18-20, вторые входы которых соединены с выходами инверторов 1113. Выходы соответствующих элементов

И 14-16 и 18, 19, 20 объединены элементами ИЛИ 21-23.

При нормальной работе блоков памяти 2-4 на всех шинах управления 10 потенциалы соответствуют логическому нулю. В соответствии с этим заперты элементы И 6-8 и 14-16, а элементы И 18-20 открыты, так что обращения (запись и считывание информации) происходят к блокам памяти 2-4 °

При отказе, например, блока памяти

2 на управв .ющую шину, соединенную с этим блоком, подается потенциал, соответствующий логической единице.

При этом открыты элементы И б и

14 и закрыт элемент И 18, информация из отказавшего блока 2 не выдается. Одновременно резервное одноразрядное ЗУ 5 оказывается подключенным ко входным шинам (шинам записи 9) и выходным шинам. Так как резервный, одноразрядный блок 5 подключен и к выходам блока выборки адресов 1, то он фактически зайимает место блока 2, т ° е. вместо обращения к отказавшему разряду происходит фактически обращение к исправному разряду блока памяти

5.

Предлагаемое устройство имеет -следующие преимущества перед известными

1. Отсутствуют сложные управляющие узлы, все схемы управления могут быть выполнены на стандартных логических микросхемах.

l0 Запоминающее устройство с автоматическим восстановлением работоспособности, содержащее блок выборки адресов, основные одноразрядные блохи памяти, шины записи и шины уп")б равления — по числу разрядов хранимой информации, резервный одноразрядный блок памяти, адресные входы основ. ных и резервного одноразрядного блока памяти подключены к выходам блока

20 выборки адресов, соответствующие шины записи соединены со входами 3aпись 1 основных одноразрядных блоков памяти, о т л и ч а ю щ е е с я тем, что, с целью упрощения и повышения

25 быстродействия схемы, в нее введены инверторы, три. группы элементов И и элемент ИЛИ, первые входы элементов

И первой группы соединены с шинами записи соответствующих разрядов, вто30, ые входы соединены с соответствующими шинами управления,>со входами инверторов и с первыми входами соответствующих элементов И второй группы,. а выходы элементов И первой груп35 ты через элемент ИЛИ вЂ” со входами Запись резервного одноразрядного блока памяти вторые входы эле) ментов И второй. группы соединены с выходом резервного одноразрядного

40 блока памяти, первые входы элементов

И третьей группы соединены с выходами основных одноразрядных блоков памяти, вторые входы — с выходами инверторов, а выходы соответствующих эле 5 ментов И второй и третьей групп соединены с соответствующими входами э. )ементов ИЛИ.

Источники информации, принятые во ,, внимание при экспертизе:

1. Бруевич Н. Г. и доступов d3. Г.

Основы теории счетно-решающих устройств, (4., Сов.Радио, 1964, с.74-75.

2. Авторской свидетельство СССР

Р 237463, 6 06 Р 11/ОО, 1965.

591966

Составитель В. Гордонова

Техред С,Беца Корректор Л. Небола

Редактор Б.Федотов

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Закаэ 604/48 Тираж,7 17 Подписное

ЦНИИПИ Росударственного комитета Совета Министров СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5