Делитель частоты с нечетным коэффициентом деления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Респубпик (»)592015

ВПТБ

Фаий аианР1нн (61) Дополнительное к авт. свид -ву (22) Заявлено 130276(21) 2323117/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 050278.Бюллетень № 5 (45) Дата опубликования описания 250178.

2 (51) М. Кл.

Н 03 К 23/00

Гаацаротеаннын яояатет

Воаата Мниаатраа GGCP яа делая яаоаретеяяя я атярытня (53) УДК 621. 374.44 (088. 8) (72) Авторы изобретения.

P° . Н.Куриляк и Ю.К.Рыбин

Научно-исследовательский институт электронной интроскопии (7а) Заявитель при Томском ордена Октябрьской Революции и ордена Трудового Красного Знамени институте им. С.М.Кирова (54} ДЕЛИТЕЛЬ ЧАСТОТЫ С НЕЧЕТНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Настоящее изобретение относится к вычислительной: технике, может найти применение в цифровых вычислительных устройствах, в частности в системах фазовой автоподстройки частоты.

Известен делитель частоты с нечетным коэффициентом деления, содержащий двоичный счетчик (1) .

Недостатком этого делителя частоты является низкое быстродействие при .сохранении скважности выходных импуль сов, равной двум, при нечетном коэффициенте деления.

Наиболее близок к предлагаемому, делитель частоты с нечетным коэффициентом деления, содержащий переключа-. тель, управляющий триггер и двоичный счетчик, соединенные в кольцо (2) .

Недостаток. данного делителя частоты - низкое быстродействие и невозмож- щ ность получения выходной последователь ности импульсов со скважностью, равной двум.

Цель. изобретения — обеспечение возможности получения, выходных импульсов сс скважностью, равной двум,.при одновременном повышении. быстродействия.

С этой целью в делитель частоты с нечетным коэффициентом деления, содержащий переключатель, управляющий триг-з0

2 гер и двоичный счетчик,-соединенные в кольцо, введен дополнительный переключатель, управляющие входы которого соединены с управляющими входами основного.переключателя и подключены к прямому и инверсному выходам двоичного счетчика импульсов, сигнальные входы соединены с сигнальными входами основ» ного переключателя и подключены к прямому и инверсному входам устройства, а выход — с нулевым входом управляющего триггера, единичный вход которого подключен к выходу основного переключат ел я.

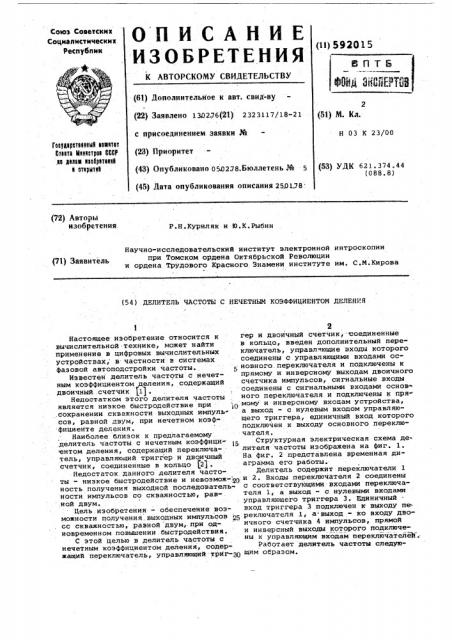

Структурная электрическая схема делителя частоты изображена на фиг. 1.

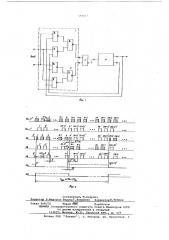

На фиг. 2 представлена временная диаграмма его работы.

Делитель содержит:переключатели 1 и 2. Входы переключателя 2 соединены с соответствующими входами переключателя 1, а выход - с нулевыми входами управляющего триггера 3. Единичный вход триггера 3 подключен к выходу переключателя .1, а выход - ко входу двоичного счетчика 4 импульсов, прямой и инверсный выходы которого подключены к управляющим входам переключателеат.:

Работает делитель частоты следующим образом.

5 3 2() ) 5

На сигнальные нходы переключателей

1 и 2 поступают прямая О и инверсная 1 последонательности. импуль.сов с периодом повторения Т . В зависимости от состояния выходного триг- гера двоичного счетчика 4 импульсов переключатели подают на управляющий триггер 3 прямую или инверсную после.довательность импульсов.

На фиг. 2 условно показано соот- 10 нетствие поступления на единичный вход триггера 3 прямой последовательности входных импульсов лри нулевом выходе дноичного счетчика, который был ранее переведен в исходное состояние им- I5 ! пульсов О инверсной последовательности через время задержки 2

Примем для удобства рассуждений, что время задержки, определяющее переходные процессы в устройствах, от 20 входа переключателей 1 и 2 до входа счетчика 4 импульсов - точки 2а (фиг.2) и ст этой точки до выхода двоичного счетчика 4 импульсов равно Г . Таким образом, к единичному входу управляющего триггера З.подключена лря25 мая последовательность входных импульсон, причем ее первый импульс. 1 подтверждает состояние управляющего триггера 3 на интервал времени т =О, 5 Твх.

После этого первым импульсом 1 инверсной последовательности, поступающим на нулевой вход триггера 3 (точка 2б на фиг.2), он переводится н противоположное состояние, т.е. устанавливается 0 . Импульсом 2 прямой последовательности триггер 3 переводится в состояние 1 . Далее импульс 2 инверсной нходной последовательности устанавливает управ" 4" ляющий триггер 3 в состояние О и

r,ä.

В момент прихода импульса ) прямой; входной .последовательности триггер 3 устанавливается в состояние"1", 45 и на выходе двоичного счетчика 4 (точка 4а на фиг.2) появляется сигнал .

I Ф I

1 . При этом переключатели 1 и 2 подключают к единичному входу инверсную, а к нуленому входу управляющего 50 триггера 3 прямую последовательность входных импульсов.

Импульс N инверсной последовательности не изменяет состояния вы55 хода триггера 3 (точка За на фиг. 2) на время т,н = 0,5Tâ„. СлецУющий (Й 1) импульс ийверсной лоследо1 вательности изменяет состояние триггера 3. Отрицательный фронт образовавшегося на выходе триггера 3 (точка За на фиг. 2) импульса (N +1) инверсной последовательности опять оказывается сдвинутым на время Ф2 = 0,5Tв„ относительно импульса N лрямой последовательности. Этот сдвиг сохраняется в течение второго полупериода выходного импульса двоичного счетчика 4 импульсов, ныход которого (точка 4а на фиг. 2) изменяет свое состояние через N входных импульсов наI чиная с (hl +1), т.е. этот импульс инверсной последовательности будет под номером (2 М +1) и т.д.

Таким образом, длительность .единичной и нулевой палунолн выходного сигнала одинакова, что соответствует скважности 2, а период повторения

)вых К) в t) т = (2N+1)T х . В описываемом делйтеле частоты триггер 3 запускается ло раздельным входам, что определяет повышенное быстродействие делителя частоты.

Формула изобретения

Делитель частоты с нечетным коэффициентом деления, содержащий переключатель, управляющий триггер и двоичный счетчик, соединенные в кольцо, отличающийся тем, что, с целью обеспечения возможности получениR выходных импульcoB со скважностью, равной двум, при одновременном повышении быстродействия, в него введен дополнительный переключатель, управляющие входы которого соединены с управляющими входами основного переключателя и подключены к прямому и инверсному.выходам двоичного счетчика импульсов, сигнальные входы соединены с сигнальными входами основного переключателя и подключены к прямому и инверсному входам устройства, а выход — c нулевым входом управляющего триггера,, единичный вход которого подключен к выходу оонбвного переключателя.

Источники информации, принятие но внимание лри экспертизе:

Авторское свидетельство СССР

9 484645, Н 03 К 23/24, 1973 °

2. Авторское свидетельство СССР

373890, Н 03 К 23/02, 1973. гт8„Д

8я„д

Н-1 Н Н+1 а+2 Н+Р

2Н 2341 2N>2 2Н+Э

И -ППП.22 (rr--i) щ (н() (1(+2)

Д (2w+r) (2Н+2)

Я Д (р р,р и щ н я+1) (и г)

Составитель М.Аудриич

Редакто Б.Федоров Tez ед Г.Коюденко Ко екто П.тулина

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 609/50 тираж /О6 Подниснсе

ЦИИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра чаская наб. . 4 5