Адресный формирователь для интегрального постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

О П И С-М" Й И Е

ИЗОБРЕТЕНИЯ

00 59325О

Сои7з Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 26,12.75 (21) 2308586/18-24 с присоединением заявки _#_ (51) M. Кл G 11С 7/00

Саве л Мнмис ров СССР по делам изобретений

И О7КРМ7ий (43) Опубликовано 15.02.78. Бюллетень № 6 (45) Дата опубликования описания 22.02.78 (53) УДК 681.327.66 (088,8) (72) Авторы изобретения

Ю. И. Щетинин, В. В. Воробьева-, В. Я. Кремлев, П. С. Приходько и О. Р. Щербинина (71) Заявитель (54) АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ ДЛЯ ИНТЕГРАЛЬНОГО

ПОСТОЯ Н НОГО ЗАПОМИ НАЮЩЕГО УСТРОЙСТВА

Гасударственный комитет (23) Приоритет

Изобретение относится к вычислительной технике, в частности к интегральным постоянным запоминающим устройствам (ПЗУ).

Известны адресные формирователи, выполненные по схеме основного элемента транзисторно-транзисторной логики (11, Наиболее близким к изобретеншо техническим решением является адресный формирователь, содержащий три транзистора, диод, два резистора, входную и выходную шины, шину питания и шину нулевого потенциала, причем база первого транзистора соединена с входной шиной, коллектор соединен с базой третьего транзистора и через первый резистор — с шиной питания, эмиттер соединен с базой второго транзистора и через второй резистор — с шиной нулевого потенциала, эмиттер третьего транзистора соединен с анодом первого диода, катод которого соединен с выходной шиной и коллектором второго транзистора, эмиттер которого соединен с шипой нулевого потенциала (2). Однако известный формирователь имеет низкое выходное сопротивление в режиме записи информации.

Целью изобретения является повышение HBдежности и уменьшение потребляемой мощности в режиме записи информации. В описываемом формирователе это достигается тем, что он содержит четвертый и пятый транзисторы, второй и третий диоды, третий, четвертый и пятый резисторы, причем эмиттер пятого транзистора соединен с коллектором третьего транзистора, коллектор соединен с шиной питания, а база — через третий резистор с шиной пита5 ния и коллектором четвертого транзистора, эмиттер которого непосредственно, а база через пятый резистор подключены к шине нулевого потенциала и аноду второго диода, катод которого соединен с выходной шиной, анод

10 третьего диода через четвертый резистор подключен к базе четвертого транзистора, а ка-.од — к шине питания.

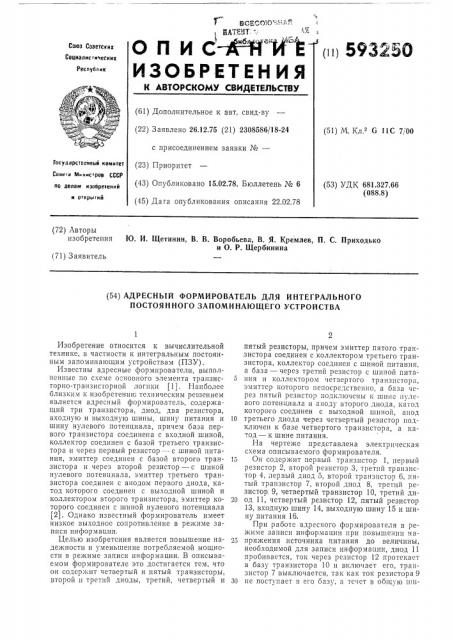

На чертеже представлена электрическая схема описываемого формирователя.

15 Он содержит первый транзистор 1, первый резистор 2, второй резистор 3, третий транзистор 4, первый диод 5, второй транзистор 6, пятый транзистор 7, второй диод 8, третий резистор, 9, четвертый транзистор 10, третий ди20 од 11, четвертый резистор 12, пятый резистор

13, входную шину 14, выходную шину 15 и шину питания 16.

При работе адресного формирователя в режиме записи информации при повышении на25 пряжения источника питания до величины, необходимой для записи информации, диод 11 пробивается, ток через резистор 12 протекает в базу транзистора 10 и включает его, транзистор 7 выключается, так как ток резистора 9

30 пе поступает в его базу, а течет в общую шп593250

Составитель В. Гуркина

Техред А. Камы пникова

Корректоры Е Хмелева и Л. Денискина

Редактор Л. Тюрина

Подписное

Изд. № 236 Тираж 788

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Заказ 110/16

Типографяя, пр. Сапунова, 2 ну через вклloчсииый транзистор 10. В рсзультатс этого ток, протекающий через диод 8, определяется величиной резистора 2 и имеет небольшую величину, что позволяет ограничивать значение выходного напряжения.

Известные ПЗУ в зависимости от их информационной емкости могут содержать десять и более адресных формирователей, выполненных по обычной планарной технологии, используемой прп производстве полупроводниковых интегральных схем.

Формула изобретения

Адресный формирователь для интегрального постоянного запоминающего устройства, содержащий три транзистора, диод, два резистора, входную и выходную шины, шину питания и шину нулевого потенциала, причем база первого транзистора соединена с входной шиной, коллектор соединен с базой третьего транзистора и через первый резистор — с шиной питания, эмиттер соединен с базой второго транзистора и через второй резистор — с шиной нулевого потенциала, эмиттер третьего транзистора соединен с анодом первого диода, катод которого соединен с выходной шиной и коллектором второго транзистора, эмиттер которого соединен с шиной нулевого потенциала, отл ич а и щийся тем, что, с целью повышения надежности и уменьшения потребляемой

5 мощности в режиме записи информации, он содержит четвертый и пятый транзисторы, второй и третий диоды, третий, четвертый и пятый резисторы, причем эмиттер пятого транзистора соединен с коллектором третьего

10 транзистора, коллектор соединен с шиной питания, а база через третий резистор — с шиной питания и коллектором четвертого транзистора, эмиттер которого непосредственно, а база через пятый резистор подключены к шине ну15 левого потенциала и аноду второго диода, катод которого соединен с выходной шиной, анод третьего диода через четвертый резистор подключен к базе четвертого транзистора, а катод — к шине питания.

20 Источники информации, принятые во внимание при экспертизе

1. Наумов Ю. E. Интегральные логические схемы. М., «Советское радио», 1970, с. 245—

249.

25 2. Каталог фирмы «Harris semiconductor», 1973, с. Ме 19 — 22, 39 — 46.