Дельта-декодер с экспандированием

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (» 594583 (61) Дополнительное к авт. свид-ву (2 ) ЗаЯвлено 02.07. 76 (21)23791 "3/18-09 с присоединением заявки М (23) Приоритет (43) Опубликовано 25.02.78. Бюллетень 3 е7 (45) Дата опубликования описания 25.0т .70, ! (51) М К., H 03 К 13/22

Н04- ) 3 18

Государственный комитет

Совета Министров СССР по делам иэооретеннй и открытий (53) УДК 621,376..55 (088,8) (72) Автор изобретения

А, Р. Шпигель

Центральный научно-исследовательский институт связи (Одесский отдел) (71) Заявитель (54) ДЕЛЬТА-ДЕКОДЕР С ЭКСПАНДИРОВАНИЕМ

Изобретение относится к уcTpoHcTBBM связи и может использоваться при построении колеров и декодеров В к„;!алах связи, образованных ме годом дс>1ьта-модуляции.

Извест(эн д(.!ьта-декодер, содержащий формн роватсль цифрового сигнала, анализатор цифрового си!.нала, элементы И, амплитудный модулятор, амнлитудн )-широтный преобразовагель, генератор тока и интегратор (1).

Однако известный дельта-декодер имеет недостаточную точность декодирования.

Цель изобретения — повышение точности декодирования.

Для этого в дельта-декодер с экспандированием, содержащий формирователь цифрового сигнала, на один вход которого подан сиг.нал «Знак прира(цения», а на другой — сигнал «Частота дискретизации», выходы которого подключены ко входам анализатора цифрового сигнала и к первым входам соответствующих элементов И, выходы которых через генератор тока подключены ко входу интегратора, введены двоичный реверсивный счетчик, ключи и генератор импульсных последовательностей, при этом выходы анализатора цифрового сигнала подкл!очены к счетному и управляющему вхолам двоичного реверсивного счетчика, Выходы которого подключены к управляю(цим входам соответствующих кл!очей, сипгальные

Входы которых соединены с соответств !olllll,чн

Выходами генератора нмпу,lbcHhlx пос,>един;1T(Л ЬНОСтЕ й, а Bbl X 0 bl К, (IO>IC I) 0 1 IC I!0>I Cl i bi !

> горыч Входак! элеxIBHToR И.

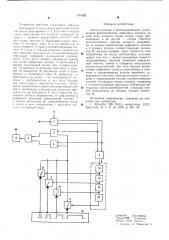

1)я чертеже дана структхрная э 1(. кт!)!!чсc.Вя схема предлагасчого устройства.

Дельта-декодер с экспандированием cî,i(ржит формllроВате,(ь 1 ц11фрОВОГО сllгнал<1, Выходы которого подключены ко 1Зхода)! ана,!нз;1тора 2 цифрового сигнала и к i!cpnb>)i Вход;(ч соответствч)ощих элементов !1 3 и -1, Выходы которых ч(рез генератор 5 "ок» нодкл!очеlli,i ко входм интеграторы 6 1В.>IINHb! II рс>3(рсивный счетчик 7, кл!очи 8 — 11 l! гcícðBòîð 12 !!3!Нх,!1,iIbix последовательностей, при этом III»xnz»I;lн>н лизатора 2 цифрового сип!Н IB ноль!!о>!си!! к lBTHO313 ll ПР(3 !3 1 ЯЮ!ЦСЧ 3 BXO;1BX! . 1Во(IЧ Н01 О рс13ерсн13ного c>IBT>IIII(B 7, 13; IxoTbi l(oT01)OI о i!0,1ключены к управляк)!цим входам соответстнук>->1) щих клlочей 8 — 1 1, сl! I нальные Входы l(OTOpb!x соединены с соответствующими Выхода ми генератора 2 Ilìïóëhcíhix носледоватсл! нос гсй. а выходы ключей 8 — ! подключены ко !)торн!): входам эле.!е ITQB И 3 н -!. нр!! этом двоичный реверсивный счетчик 7 с,> тент из цепочки трнг 25 геров 13--16.

Устройство работает следующим образом.

Л ализатор 2 «н«лидирует двсичпый сигнал на ьыхоlå формирователя 1. Если число подряд следующих единиц илп и лей нс г1агвь:шает чегыр», т :: воичном реверсивноA1 счетчике 7 взве ден только триггер !3. Выходной сигнал триггеры 13 отпирает ключ 8 и на интегратор 6 через генератор 5 тока и соответствуюший элемент И 3 или 4 каж сый интервал дискретизации проходят импульсы из последовательности импульсов, имеюсцей минимальную длительность. Если число подряд следуюпсих единиц или нулей превышает четыре, то анализатор 2 выдает импульсный сигнал, при котором триггер 13 приходит в исходное состояние, а триггер !4 взводится. В результате клю 8 запирается, а отпирается ключ 9, пропуская свой выход (и далее — на интегратор 6) импульс с длительностьlo в iâ«раза больше, чем длите. ьность импульсов триггеры 13.Чсм число, записанное в двоичный реверсивный счетчик 7, тем больше длительность импульса, приходяпсего на интегратор 6. Если крутизны исходного сигнала понижается, то анализатор 2 переводит двоичный реверсивный счетчик 7 в режим вычитания по управляющему входу и число в нем уменьшается с приходом сиг «лы па счетный вход.

Формула изобретения

Дельта-декодер с экспандированием, содержащий формирователь цифрового сигнала, на один вход .которого подан сигнал «Знак приращения», а на другой — сигнал «Частота дискретизации», выходы которого подключены ко входам анализатора цифрового сигнала и к первым входам соответствующих элементов И, выходы которых через генератор тока подключены ко входу интегратора, отличающийся тем, что, с целью повышения точности декодирования, введены двоичный реверсивный счетчик, ключи и генератор импульсных последовательностей, при этом выходы анали15 затора цифрового сигнала подключены к счетному и управляюгцему входам двоичного реверсивного счетчика, выходы которого подключены к управляющим входам соответствующих ключей, сигнальные входы которых соединены с соответствующими выходами генератора им20 пульсных последовательностей, а выходы клк чей подключены ко вторым входам элементов И.

Источники информации, принятые во внимание при экспертизе:

1. Schindler HR Delta modulation. JEEE

Specti um, Ъ 7, iX 1О, 1970, р. 69 — 78.

UHMHHH ЗаказБ?0/5?. ! ираж 10о»6 Подписное

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4