Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистииеских

Республик (11. 594594 (61) Дополнительное к авт. саид-ву (22) Заявлено 03.05.76 (21)2355376/18-09 (51) М. Кл.2

Н 04 L 7/02 с присоединением заявки №(23) Приоритет (43) Опубликовано 25.02.78. Бюллетень № 7

Гооударотоенный коинтет

Сонета Министров СССР по делам нзооретеннй и открытий (53) УДК 621 3Р4, .662(08Р. 8} (45) Дата опубликования описания 03.02. 78 (72) Автор изобретения

Д. Г. Нисневич (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЭАЦИИ!

Изобретение относится K системам передачи и обработки дискретной информации.

Известно устройство тактовой синхронизации, содержащее на информационном входе фазовый детектор, выход которого подключен к входу усредняющего блока, и . последовательно соединенные задающий генератор и делитель частоты (1 1.

Однако известное устройство обладает невыеокоЪ точностью регулирования и боль шим временем вхождения в синхронизм.

Цель изобретения - сокращение времени вхождения в синхронизм и повышение точности регулировки.

Для этого в устройство тактовой синхр ь: 15 низации, содержащее на информационном входе фазовый детектор, выход которого подключен к входу усредняющего блока, и последовательно соединенные задающий ге чератор и делитель частоты, введены после 0 довательно соединенные формирователь сиг палов фазовых зон, блок памяти, дешифратор и элемент ИЛИ, при этом к управля ющим входам дешифратора подключены соответствующие выходы делителя частоты, 2 а выход элемента ИЛИ подключен к дру гому входу фазового детектора, информационный вход которого соединен с управ ляющим входом формирователя сигналов фазовых эон, а выход усредняющего блока подключен к управляющему входу блока памяти.

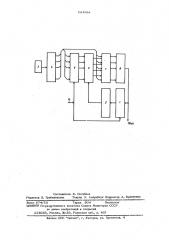

На чертеже дана структурная электрическая схема предлагаемого устройства.

Устройство содержит на информационном входе фазовый детектор 1, выход которогоi подключен к. входу усредняющего блока 2, последовательно соединенные задающий генератор 3 и делитель 4 частоты и по« следовательно соединенные формирователь

5 сигналов фазовых зон, блок 6 памяти, дешифратор 7 и элемент И ЛИ;8,приэтом к управляющим входам дешифратора 7 подключены соответствующие выходы делителя 4 частоты, а выход элемента ИЛИ 8 подключен к другому входу фазового детектора 1, информапиончый вход которого соединен с управляющим входом,формирователя 5 сигналов фазовых зон, а выход

3 усредняющего блока 2 подключен к управляющему входу блока 6 памяти, Устройство работает следующим образом.

Формирователь 5 сигналов фазовых зон представляет собой дешифратор, на вход которого поступают параллельный код от делителя 4. частоты и входной сигнал.Число входов формирователя 5 m= а+1 {или .2n i k ), где д - количество разрядов делителя 4 частоты, а число выходов Кравно количеству реализуемых устойчивых состояний делителя 4 частоты, определяемых модулем коэффициента деления последнего. Выходы формирователя 5 возбуждаются при установке в соответствующее положение: делителя 4 частоты и наличии входного сигнала U . Импульсы, появ ляющиеся на смежных выходах формирователя 5, разнесены по фазе на величину Л f= - и разделяют период выК ходных колебаний на соответствующие зоны. Благодаря такому построению схемы сигнал вырабатывается только на том выходе формирователя 5,; который синфаэен с входным сигналом U<

Блок 6 памяти представляет собой регистр с параллельной записью информации, количество разрядов которого равно числу выходов формирователя 5. Блок 6 памяти зо работает в двух режимах: з писи информации и хранения информации.

Режим записи информации осуществляется при поступлении DT усредняющего блока

2 на управляющий вход блока 6 памяти 3s сигнала разрешения записи, При этом код, поступающий от формирователя 5 на j информационные входы блока 6 памяти, переписывается в разряды последнего и запоминается им, 4О

В режиме хранения информации с выхода усреднаю .,его блока 2 на управляющий вход блока 6 памяти поступает запрет записи. Последний хранит ту информацию, которая была введена в него при послед- 45 ней записи информации.

B установившемся .режиме сигналы U< ии синфазны, фазовый детектор 1 регистрирует отсутствие рассогласования, с выхода усредняющего блока 2 на управ ляющий вкод блока 6 памяти поступает сигнал запрета- записи информации. Блок

c)4

6 памяти находится и режиме хранения и фаза колебаний Ч,Х остается неизменЬМХ ной. При расхождении по фазе коле.— баний U u U фазовый детектор 1 вырабатывает соответствующий сигнал, поступающий на усредняющлй блок 2. С выхода последнего на управляющий вход блока 6 памяти поступает сигнал разрешения записи информации. Код с выходов формирователя 5 переписывается в блок 6 памяти и запоминается им. При этом создаются условия для возбуждения того выхода дешифратора 7, сигнал на котором синфазен с входным сигналом U

Устройство переходит в режим удержания, Как видно из описанного вьине, процесс подстройки в предлагаемом устройстве оптимален. В переходном режиме отсутствуют перерегулирования и колебания около положения настройки. Длительность переходного процесса не превышает одного периода частоты входного сигнала и является минимально возможной для рассматриваемого класса устройств.

Формула изобретения

Устройство тактовой синхронизации, содержащее на информационном входе фазовый детектор, выход которого подключен к входу усредняюшего блока, и последовательно соединенные задающий генерагориделитель частоты, о т л и ч а ющ e e с я тем, что,слельюсокрашениявремели вхождения в синхронизм и повышения точности регулировки, введены последовательно соединенные формирователь сигналов фазовых зон, блок памяти, дешифратор и элемент ИЛИ, при этом к управляющим входам дешифратора подключены соответствующие выходы делителя частоты, а выход элемента ИЛИ подключен к другому входу фазового детектора, инфор» мационйый вход которого соединен с управляющим входом формирователя сигналов фазовых зон, а выход усредняющего блока подключен к управляющему входу блока памяти.

Источники информации, принятые во внимание при экспертизе:

l. Авторское свидетельство СССР

l4 489238, кл. Н 04 Ь1/04, 1973.

Составитель Е. Погиблов

Редактор Л. Гребенникова Техред "Н. Андрейчук Корректор A. Кравченко

«ЗЮЗЮ :3» ЙЗЗЪ|, -4ФИЗ Вй М3Ю сМФЮВ%4:-йаВ

Заказ 874/53 Тираж 804 Подписное

БИИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий, 113035, Москбб, Ж-35, Рарасааа наб;, д, 4/5

Филиал ППП Патент, г, Ужгород, ул, Проектная, 4