Устройство для тактовой синхронизации с регенерацией дискретных сигналов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е )ве4вев

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.05.76 (21)2359643/18-0 (51) М. Кл. с присоединением заявки Ме (23) Приоритет (43) Опубликовано25. 02.78. Бюллетень М7 (45) Дата опубликования описания07.03. Г3

Н 04 L 7/04

Государственный комитет

6аввта 1йинистрав СССР по делам изобретений и открытий (53) УДК62 1. 394. 662 (088,8) (72) Автор изобретения

В. П. Леонов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ

С РЕГЕНЕРАЦИЕЙ ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится к радиотехнике и может использоваться в системах радио- и проводной связи, телемеханике, вычислительной технике, в системах автоматического управления.

Известно устройство для тактовой синхронизации с регенерацией дискретных сигналов, содержащее на информационном входе фазовый дискриминатор, выходы которого через управляющий блок, к другому входу которого подключен выход задающего генератора, под; ключены ко входу счетчика, один из выходов которого подключен к другому входу фазового дискриминатора, а другие выходы счетчика через дешифратор подключены ко входу выходного блока памяти (11.

Однако в известном устройстве при искажениях типа «дробления» и импульсных помехах возможно искажение регенерации принимаемых сигналов.

Цел ь изобретения — повышение помехоустойчивости при наличии импульсных помех и искажений типа «дробления».

Для этого в устройство для тактовой синхронизации с регенерацией дискретных сигналов, содержащее на информационном входе фазовой дискриминатор, выходы которого через управляющий блок, к другому входу которого подключен выход задающего генератора, подключены ко входу счетчика, один из выходов которого подключен и другому входу фазового дискриминатора. а другие выходы счетчика через дешифратор подключены ко входу выходного блока памяти, введены дополнительный дешифратор и п блоков памяти, где и = 1, 2, 3 ..., при этом дополнительные выходы дешифратора через соответствующие блоки памяти. другие входы которых подключены к информационноlO му входу фазового дискриминатора, подключены к соответствующим входам дополнительного дешифратора, выход которого подключен к дополнительному входу выходного блока памяти.

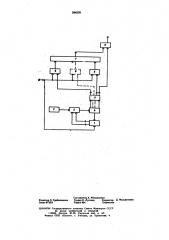

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство для тактовой синхронизации с регенерацией дискретных сигналов содержит на информационном входе фазовый дискриминатор 1, выходы которого через управляющий блок 2, к другому входу которого подключен выход задающего генератора 3, подключены ко входу. счетчика 4, один из выходов которого подключен к другому входу фазового дискриминатора 1, а другие выходы счетчика 4 через дешифратор 5 подключены ко входу выходного блока 6 памяти, дополнительный дешифратор

2а 7 и и блоков 8 памяти, где п= 1, 2, 3

594595

Устройство работает следующим образом.

Импульсы задающего генератора 3 через управляющий блок 2 поступают на счетный вход счетчика 4. Выходные импульсы счетчика

4, период повторения которых равен длительности посылки, поступают на вход фазового дискриминатора 1. Эти импульсы служат опорным напряжением фазового дискриминатора 1.

На другой вход фазового дискриминатора 1 со входа устройства поступают принимаемые информационные посылки. По фронтам информационных посылок, поступивших при действии одного, например, отрицательного полупериода опорного напряжения, фазовым дискриминато-" ром i вырабатывается команда на добавление управляющим блоком 2 одного внеочередного импульса, а По фронтам информационных посылок, поступивших при действии другого, например, положительного полупериода опорного напряжения, фазовым дискриминатором 1 вырабатывается команда на исключение управляющим блоком 2 одного импульса. Каждое добавление внеочередного импульса приводит к уменыпению времени заполнения счетчика 4, а исключение импульса — к увеличению времени заполнения счетчика 4; Динамическое повторение процесса добавлении н исключения импульСов поддерживает равенство фронтов информационных посылок в течение одно о и другого полупериодов информационных посылок. Таким образо1и обеспечивается автоматическое слежение отрн4ательиого перепада опорного напряжения за фронтом принципиальной посылки.

Поэтому каждому состоянию счетчика 4 соответствует вполие определенная фаза принимаеьщй информационной посылки.

Формула изобретекия

Устройство для тактовой синхронизации с регенерацией дискретных сигналов, содержа- щее на информационном входе фазовый дискриминатор, выходы которого через управляющий блок, к другому входу которого подключен выход задающего генератора, подключены ио . входу счетчика, один пэ выходов которого подключен к другому входу фазового дискрвмииа. тора, а другие выходы счетчика через деиафратвр подключены ко моду выходного блока памяти, отличающееся тем, чю, с нелло повышения помехоустойчивости ярк наличии импульс@ ных помех и искажений типа «дробления», введены дополнительный: дешифратор и в блоков памяти, где п 1, 2, 3, ..., при этом дополнительные выходы даиифратора через соответствующие блоки памнти, другие входы которых подключены к информационному входу фазового дискриминатора, подключены к соответствующим входам дополнительного дешифратора, выход которого подключен к дополнительному входу выходного блока, памяти.

Источники информации, принятые во анимачя нне при экспертизе:

I, Мартынов Е. М; Синхронизация в системах передачи дискретных сообщений, М,, «Связь», 1972. при этом дополнительные выходы дешнфратора

5 через соответствующие блоки 8 памяти, дру;

r.ле входы которых подключены к информационному входу фазового дискриминатора 1, подключены к соответствующим входам дополнительного дешифратора ?, выход которого подключен к дополнительному входу выходного блока б памяти.

Состояние счетчика 4 через дешифратор 5 преобразуются i синхроимпульсы, ноторые вырабатываются через равные промежутки времени. Первый сиихроимпульс соответствует началу информационной посылки, а последний-ее концу. Синхроимпульсы с выходов дешифратора 5 поступают на записывающие входы блоков 8 памяти (функцию блоков памяти может выполнять триггер со счетным входом). Яа информационный вход блоков 8 памяти поегупаки информационные посылки. В первый блок

8 памяти записывается состояние информационной посылки в момент первого синхроимпульса, во второй — в момент второго снихроимпульса и т. д. Выходы блоков 8 памяти соединены со входами дополнительного дешифратора

7. На выходе дополнительного дешифратора

7 вырабатывается сигнал, соответствующий состоянию большинства блоков 8 памяти. Таким образом в блоках 8 памяти принимаемый сигнал квантируется, а затем интегрируется дешифратором 7.

С выхода дешифратора 7 сигнал поступает на информационный вход. выходного блока

6 памяти. На его записывающий вход поступает синхроимпульс, соответствующий фронту принимаемой посылки, и переписывает состояние выхода дешифратора 7 в выходной блок 6 памяти. В выходном блокс 6 памяти записанная

И информация сохраняется в течение следующей элементарной посылки. Состояние выходного блока 6 памяти определяет символ регенерированной посылки.

Воздействие помех в течение следования менее половины количества синхроимпульсов каждой посылки ие исказит регенерированную информацию, так как в большинстве блоков

8 памяти будет записана истинная информация, а по состоянию большинства входов дополнительный дешифратор 7 произведет правильную регенерацию.

Составмтель Л. Мемыинкова реликтов Д. Гребеиинкова,Техред О. Луговин Корректор д. вин"емки

Заказ 613/53 Тмраж 804 - Поднисное глНИИПИ Государственного. комитета Совета Министров СССР ио . делам изобретений и открытий

I ) 3035, Москва, Ж-35, Раушская наб. д. 4/Ь

Филиал ППП «Патент», г. Ужгород, ул. Проектная. 4