Линейный интерполятор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ к лвтоискомм свидетельствь пщ 5 95706

Союз Советских

Социалис1ических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 21.12.76 (21) 2432831/18-24 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано 28.02.78. Бюллетень № 8 (45) Дата опубликования описания 04.03.78 (51) М. Кл. G 05B 19, 18

Государственный комитет

Соне а MvtlHc epos СССР

Ао делам изобре1ений и открытий (53) УДК 621.503.55 (088.8) (72) Авторы

Г. В, Добрис, P. Ф. Федоров, А. И. Пашенцев, Г. Я. Кузьмин, Б. К. Левин и В. A. Ратмиров изобретения (71) Заявитель (54) ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР

Изобретение относится к вычислительной технике и может быть использовано в системах числового программного управления станками.

Известен линейный интерполятор, состоящий из регистра подынтегральной функции, делителя частоты, пересчетной схемы и вентилей (1).

Недостатком этого иптерполятора является ограничснг ое повышение точности при увеличении емкости регистров, так как ошибка интерполятора растет с увеличением числа разрядов регистров.

Наиболее близок по технической сущности к изобрстенгпо линейный интерполятор, содержащий блок задания программы, выходы которого подключены к входу регистра подыптегральпой функции п к входу блока задания скорости, другой вход которого соединен с выходом генератора тактовых импульсов (2).

Та кой интер полятор также имеет низкую точность.

Цель изобретения — повышение точности интерполятора.

Это достигается тем, что в интерполятор дополнительно введены блок счетчиков, блок сравнения и генератор псевдослучайных чисел, причем выход блока задания скорости присоединен и первым входам блока сравнешгя и входу генератора псевдослучайных чисел, выходом подключенного к вторым входам блока сравнения. к третьим входам которого присоединены выходы регистра подыптегральной функции, а выходы блока сравнения соединены с соответствующими входами блока счетчиков.

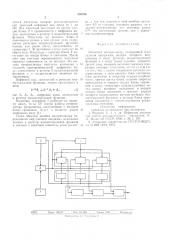

Структурная схема интерполятора представлена на чертеже.

Опа содержит генератор 1 псевдослучайных чисел, блок 2 сравнения, регистр 3 подынтегральной функции, блок 4 счетчиков, блок 5 задания программы, блок 6 задания скорости и генератор 7 тактовых импульсов.

15 Интерполятор работает следующим образом.

Перед началом операции линейного интерполирования от блока 5 заносится двоичный цифровой код, соответствующий отрабатыва20 емой прямой, в регистр 3 подынтегральной функции, а блок 4 счетчиков устанавливается в нулевое состояние. После включения генератора 7 нмпульсы от него начинают поступать на блок 6, который задает требуе25 мую скорость работы устройства, подавая тактовую последовательность импульсов на входы блока 2 сравнения и генератора 1.

На выходах генератора 1, представляющего собой семиразрядный сдвиговый регистр

30 с линейной обратной связью, начинают появ595706

Из -(Xl! 205

1 11ра>(1047

)1()!(1)н(7:Î(.

Заказ 108/17

НПО! 1 1 1 1 и 1 а ; 1 (1 1 1 1 1, 1 1 1 > 1 . I : : (1 1 (> 1 1 I, «), 1ЯТ !>CЯ fi.(1ПX Г(ЬСЫ, KOТОР ЫC PЯСС!(1 ЯТРиf;! IOТСЯ кяк дво !чпый цифровой Koч чисел от 1 до

127. Эти иъ!Пул! Сы поступ!!1от ия группу Входов блока 2 и срявпш)аются с цифровы кодом, занесенным в регистр 3 подыптсгральиой функции. Импульсы пя выходах блока 2

ИОЯВЛ ЯIОТСЯ ТОЛЬКО 13 !0>! СЛУЧЯС, (. CË I! СЭДСР

>кимос регистров подыптсгряльпой фу1.кции болыис или равно числу, поступившему от генератора 1. В противном случяс импул >с ие образуется. Импульсы с Выходов блока 2 noc7óï»10ò па входы блока 4 счет !иков. После того как счетчики переполняются, импульсы г;ереноса появляются иа их выходах. IIll Bhl. Оде интерпол я Гор(! II. >I пу(1ьсь1 Возник» !От с частотой, пропорциональной цифровому Коду, записанному в регистр 3 подыптсгральиой функции, T. с. осуществляется линейная интерполяция.

ЦпфРОВ011 КОД, B»BI!Cell! ПЫЙ В РЕГ ICTPС ПОД ьп(гсгряльпой функции, можно llpc;fcTBB ITh в

13ИДС

-2 "А, +2 — А, + А„ 11) где А1, Аа, А. — цифровыс коды, записанные в регистр подынтегральпой функции.

Поскольку генератор 1 работает по полному циклу, то за 127 тактов работы иитерполятора приращения, поступгпощие с выходов бл о и;1 C p» 13 I I C I I I 1 31, цифровому коду (1) .

Таким образом, ошибка иптсрполяторя определяется округлением вводимых начальных данных в регистр подынтегр -1.7hfiîé функции и связала с конечной емкостью этого регистР Я, !1 так 1(lK . >1»кс11>1м. этОЙ 0IIIIfO K!I cocTBBлист 0,5 OT единицы младшего разряд I, то г, дяпиом f1!IT(ðïîëÿTîð(. этя Величина рави»

2-"-, и о зпя штельпо мсиьшс, чем у известб Iihfx иитерполяторов. (1)оp >3 7(l и 300?cтспIIЯ

Л ипс1! П1>IЙ питсp ilo;i H I op, (Одср)каши Й 0.10«

;3ЯДГ1ПИЯ ПРОГРЯ ..I >IÛ, BBIKOÄÛ KOTOPOÃÎ ПОДключспы к Входу регистра подыитсгряльиой функции и и Входу б !ока задания скорости, ДРУ!ОЙ БХОД KO 1 OPOÃO СОС;(ИПСП С БЫХОДОМ ГСПЕР Я ТОР» Т!1КТОБЬ!Х П . > ПХ, IT>CO!3, 0 Т 7 ll 1 Я О Щ 11 11 (я тем, iTO> с целью повышения то(ности ипТ PПО, IЯТОРЯ, 13 1!CГО 13Б ;IС11Ь1 0.70К С 1(Т 1ИKOБ, олок сряьч(спия и гелерllTop псевдослучайных

20 чисел, причем Выход олока задания скорости присоеди:!сп к пср13ым ..подам блока сравнения il Вход3 Гепсp»TGpя пссВдосл> чяЙных чи сел, Выход которого подключен к вторым

Вход!!м 0,70кя срявпснпя, K третьим Входам

25 которого рисосдипс:1ы Выходы регистра подыитегряльпой функции, l гыходы блока сравнения соединены с скот!!стет!Зу!Ошими входа:i I f f О, O K H C 1 Ñ Ò i I i K O B .

1)с(очпики информации, 30 припять!с Бо Бпих;a»1:ñ при экспертизе

Воронов . (..)(. и др, 11ифровыс аналоги ,, 7 Я 011CT()1 !11!ТО.>!»Тн >!С(KOI 0 УПР !3.1СII И Я. . I„Из-во )11 СССР )900, с. 59, с. )76.

2..7,!3торское свидстсльс гво СССР Уо 503271, ЗЗ кл. Ci 05В 19, )8, 1973.