Устройство для управления передачей информации

Иллюстрации

Показать всеРеферат

И C-"À""ß И ih

Союз Советских

Социалистических

Республик

О П (11) 596937

И3ОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.03,75 (21) 2109791/18-24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 05.03,78. Бюллетень № 9 (45) Дата опубликования описания!0.05,78, (51) M. Кл.

& 06 Р 3/04

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.327

{ 088.8) (72) Авторы изобретения

В, Н. Блинов, В, А. Бушпя и В. Н, Сасковец (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ

Изобретение относится к вычислительной технике и может быть использовано для комплексирования микропроцессоров в вычислительну.ю систему.

Известны устройства управления передачей информации, содержащие блоки соответствующие каждому процессору, связанные общими шипами питания, причем каждый блок содержит триггера, формирователи и логические элементы (1), (2) .

Это устройство обеспечивает подключение к общей магистрали в порядке приоритетов. Недостатком этих устройств являются задержки в обслуживании менее приоритетных процессоров при решении задач одинаковой срочности.

Известные устройства не обеспечивают центральному процессору возможность эффектив- I5 но управлять очередностью обменов с периферийными процессорами.

Наиболее близким техническим решением является устройство для управления передачей информации, содержащее и логических блоков связи, первые выходы которых являются выходами устройства, второй выход каждого логического блока связи подключен к первому входу последующего логического блока связи, второй выход последнего логического блока связи соединен с первым входом первого логического блока связи, второй вход каждого логического блока связи соединен с соответствующим входом группы входов устройства (3).

К недостаткам устройства следует отнести ограниченные функциональные возможности.

Порядок и длительность подключения источников информации не могут меняться в зависимости от объема предъявляемой информации, ее важности и срочности. Такое устройство не может обеспечить эффективного построения системы обменов между процессорами вычислительной системы.

Цель изобретения — расширения функциональных возможностей, заключающееся в том. что центральный процессор может задавать lloбую последовательность подключения периферийных процессоров к общей магистрали.

Поставленная цель достигается тем, что устройство дополнительно содержит блок установки кода обмена, элемент ИЛИ, генератор, триггер блокировки и элемент И, причем выход генератора соединен с первым входом элемента

И, единичный вход триггера блокировки соединен с первым входом устройства, единичный выход триггера блокировки соединен со вторым входом элемента И, выход элемента И соединен с третьим входом каждого логического блока связи, нулевой выход триггера блокировки со596937 единен с четвертым входом каждого логического блока связи, третий выход каждого логического блока связи соединен с нулевым входом триггера блокировки, п выходов блока установки кода обмена соединены соответственно с пятым входом каждого логического блока связи, (и+ 1) выход блока установки кода обмена соединен с (и + 1)-ым входом элемента ИЛИ, вход блока установки кода обмена соединен со вторым входом устройства, и еще, отличающееся тем, что логический блок связи содержит два триггера, первый и второй элементы И, дешифратор подключения, вход которого соединен со вторым входом логического блока связи, вход тактированной установки первого триггера соединен с первым входом логического блока связи, вход асинхронной установки первого триггера соединен с пятым входом логического блока связи, вход синхронизации первого триггера соединен с третьим входом логического блока связи, единичный выход первого триггера соединен с третьим входом логического блока 29 связи, единичный выход первого триггера соединен со вторым выходом логического блока связи и первыми входами первого и второго элементов И, второй вход первого элемента

И соединен с четвертым входом логического блока связи, выход первого элемента И соединен с первым выходом логического блока связи, с нулевым входом логического блока связи и с нулевым входом второго триггера, выход дешифратора кода подключения соединен с единичным входом второго триггера, единичный выход которого соединен со вторым входом второго элемента И, выход которого соединен с третьим выходом логического блока связи.

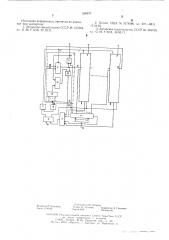

На чертеже представлена функциональная схема устройства управления передачей информации. 35

Устройство содержит и логических блоков связи 1, 2, ..., 3, блок установки кода обмена 4, элемент ИЛИ 5, триггер блокировки 6, элемент

И 7 и генератор 8. Каждый логический блок связи содержит два триггера 9, 10, два элемента И 11, 12 и дешифратор подключения 13.

Вход блока установки кода обмена 4 является входом 14 устройства. Соответствующие выходы блока установки кода обмена 4 соединены с входами 15 каждого логического блока связи 1, 2, ... 3. Общий выход блока установки кода у обмена соединен с соответствующим входом элемента ИЛИ 5, выход которого соединен с нулевым входом триггера блокировки 6, единичный вход которого является входом 16 устройства. Единичный выход триггера блокировки

6 соединен со входом элемента И 7, другой вход которог соединен с выходом генератора 8.

Выход элемента И 7 соединен с входом 17 всех логических блоков связи 1, 2, ... 3. Нулевой выход триггера блокировки 6 соединен со входами 18 всех логических блоков связи 1, 2, ... 3.

Выход 19 каждого логического блока связи, кроме последнего, соединен с входом 20 следующего логического блока связи, а выход 19 последнего логического блока связи 3 — со входом 20 первого логического блока связи !.

Выходы 21 логических блоков связи 1, 2, 3 являются выходами устройства, а их входы

22 входами устройства. Выходы 23 логических блоков связи I, 2, ... 3 соединены с соответствующими входами элемента ИЛИ 5. В каждом логическом блоке связи вход 15 соединен с входом синхронной установки триггера 9, вход

17 блока — с входом тактированного триггера

9, а вход 20 — с входом тактированной установки того же триггера 9, единичный выход которого соединен с первым входом элемента И 11, вторым входом элемента И 12 и выходом

19 блока. Вход 18 блока соединен со вторым входом элемента И 11, выход которого соединен с выходом 21 блока и нулевым входом триггера

10, подключенного единичным выходом к первому входу элемента И 12. Выход элемента

И 12 соединен с выходом 23 блока. Вход 22 логического блока связи соединен со входом дешифратора подключения 13, выход которого соединен с единичным входом триггера 10. После включения устройства управления передачей информации его работа начинается с того, что на вход 14 устройства поступает из центрального процессора определенный код, который воспринимается блоком установки кода обмена 4. Этот блок формирует сигнал, который с его общего выхода ерез схему ИЛИ 5 поступает на нулевой вход триггера блокировки 6 и устанавливает его в соответствующее состояние. Сигнал с единичного плеча триггера блокировки 6 запрещает прохождение импульсов сдвига через элемент И 7, поступающих с генератора 8. Сигнал с нулевого выхода триггера, блокировки 6 поступает на вход 18 логических блоков связи 1, 2, 3 и далее на второй вход элемента И 11 в каждом блоке, разрешая выдачу сигнала управления с выхода этого элемента. Кроме этого, блок установки кода обмена

4 формирует сигналы на выходах, соответствующих логическим блокам связи 1, 2, 3, которые поступают на входы 15 этих блоков и далее в каждом блоке на вход асинхронной установки триггера 9. Эти сигналы устанавливают триггер

9 определенного логического блока связи в состояние «1», а триггеры 9 всех остальных логических блоков связи — в состояние «О».

В выбранном логическом блоке связи разрешающий сигнал проходит с единичного выхода триггера 9 через элемент И 11. Сигнал с выхода элемента И 11 поступает на соответствующий выход устройства и осуществляет подключение требуемого периферийного устройства к общей магистрали. Между центральным устройством и выбранным периферийным устройством осуществляется обмен, требуемый для проверки исправности и начальной установки периферийного устройства. После окончания этого обмена центральное устройство таким же образом с помощью устройства управления передачей информации осуществляет поочередное подключение других периферийных устройств.

После того, как все начальные установки выполнены, на вход 16 устройства управления передачей информации подается сигнал окончания обмена, который поступает на единичный вход триггера блокировки 6 и устанавливает его в состояние «1». Соответствующий сигнал с единичного выхода триггера блокировки 6 раз596937

Формула изобретения решает прохождение импульсов сдвига с выхода генератора 8 через элемент И 7 на входы ! 7 логических блоков связи 1, 2, 3. В каждом логическом блоке связи импульсы сдвига со входа 17 поступают на вход тактирования триггера 9. Эти триггеры всех логических блоков связи образуют циклический регистр сдвига, в котором под действием тактовых импульсов циркулирует комбинация, содержащая одну логическую единицу.

Требования на обмен информацией с центральным устройством подается периферийными устройствами в виде определенной комбинации сигналов на вход 22 соответствующего логического блока связи. Эта комбинация сигналов распознается дешифратором подключения 13, который формирует на своем выходе сигнал, поступающий на единичный вход триггера 10 и устанавливает его в соответствующее состояние. Совпадение сигналов, поступающих с единичных выходов триггера 9 и 10, происходит на элементе И 12 тогда, когда в результате циклического сдвига триггер 9 данного логического блока связи оказывается в состоянии «1». Сигнал с выхода элемента И 12 через элемент

ИЛИ 5 поступает на нулевой вход триггера блокировки 6 и устанавливает его в соответствующее состояние. Сигнал с единичного плеча триггера блокировки 6 запрещает прохождение тактовых импульсов через элемент И 7. Сигнал логической «I» с нулевого плеча триггера блокировки 6 поступает на элементы И 7 всех логических блоков связи, но сигнал логической

«1» формируется только на выходе элемента

И 7 того логического блока связи, в котором триггер 9 находится в состоянии «1». С выхода элемента И 7 сигнал обеспечивает подключение периферийного устройства, подавшего требование на обмен, к общей магистрали, кроме этого сигнал. с выхода элемента И 7 поступает на нулевой вход триггера 9 и сбрасывает его.

После окончания обмена на вход 16 подается сигнал, который устанавливает триггер блокировки 6 в состояние «1». Все происходит так же, как и при окончании начальной установки.

Если за время, в которое между центральным устройством и определенным периферийным устройством происходила передача информации, другие периферийные устройства подали требования на обмен информацией, то в соответствующих им логических блоках связи произойдет установка триггера 10 в состояние «1». Обслуживание этих требований будет осуществляться в порядке циклического опроса, благодаря сдвигу логической «1» в циклическом регистре, образованном из триггеров

9 всех логических блоков связи.

Требуемая очередность подключения периферийных устройств может задаваться центральным устройством точно так же, как и при начальной установке периферийных устройств.

Устройство управления передачей информации имеет по сравнению с существующими устройствами следующие преимущества: а) обеспечивает подключение периферийных устройств по их заявкам в порядке циклического опроса;

2Е

2S

40 б) обеспечивает центральному устройству возможность задавать любую последовательность подключения периферийных устройств.

1. Устройство для управления передачей информации, содержащее и логических блоков связи, первые выходы которых являются выходами устройства, второй выход каждого логического блока связи подключен к первому входу последующего логического блока связи, второй выход последнего логического блока связи соединен с первым входом первого логического блока связи, второй вход каждого логического блока связи соединен с соответствующим входом группы входов устройства, отличающееся тем, что с целью расширения функциональных возможностей устройство дополнительно содержит блок установки кода обмена, элемент

ИЛИ, генератор, триггер блокировки и элем нт

И, причем выход генератора соединен с первым входом элемента И, единичный вход триггера блокировки соединен с первым входом устройства, единичный выход триггера блокировки соединен со вторым входом элемента И, выход элемента И соединен с третьим входом каждого логического блока связи, нулевой выход триггера блокировки соединен с четвертым входом каждого логического блока связи, третий выход каждого логического блока связи соединен с нулевым входом триггера блокировки, п выходов блока установки кода обмена соединены соответственно с пятым входом каждого логического блока связи, (n+ 1) выход блока установки кода обмена соединен с (п + 1)-ым входом элемента ИЛИ, вход блока установки кода обмена соединен со вторым входом устройства.

2. Устройство по п. 1, отличающееся тем, что логический блок связи содержит два триггера, первый и второй элементы И, дешифратор подключения, вход которого соединен со вторым входом логического блока связи, вход тактированной установки первого триггера соединен с первым входом логического блока связи, вход асинхронной установки первого триггера соединен с пятым входом логического блока связи, вход синхронизации первого триггера соединен с третьим входом логического блока связи, единичный выход первого триггера соединен с третьим входом логического блока связи, единичный выход первого триггера соединен со вторым выходом логического блока связи и первыми входами первого и второго элементов

И, второй вход первого элемента И соединен с четвертым входом логического блока связи, выход первого элемента И соединен с первым выходом логического блока связи, с нулевым входом логического блока связи и с нулевым входом второго триггера, Выход дешифратора кода подключения соединен с единичным входом второго триггера, единичный выход которого соединен со вторым входом второго элемента

И, выход которого соединен с третьим выходом логического блока связи.

596937

Составители И. Сигалов

Текрсд О., сов»я Корректор А. Гриценко ! I I f>>l >>> 82 в Подписное

Редг>кт<>р Р Киселева

3;>ê;>ç l !о !!6

1!11111!ПИ Госу.га1>сл венного ко»и>ета Совета Министров СССР по делана 113о6 f>eòå» èé Il о > к р ытий

1 I:3035, Москва, Ж-:35, Раушская иаб., д. 4/5

Фи,>иа.> ПГ111 «Патент». г, Ужгород, Ул. Проектная, 4

Источники информации, поинять!е во внимание при экспертизе:

1. Авторское свидетельство СССР № 317064, кл. G 06 F 9/18, 07.10.71.

1

2. Патент США № 3178586, кл. 307 — 88.5, 13.04.65.

3. Авторское свидетельство СССР № 394739, кл. G 06 F9/18,,30.03.71.