Частотно-импульсное множительноделительное устройство

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

О П И С А Н И Е,1,в9е9«

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИИЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 22.12,75 (21)2303459/24 (51) М. 1<л.

C 06 F 7/52 с присоелинением заявки № (23) Приоритет (43) Опубликовано 05.03.78. Бюллетень № 9 (45) Дата опубликования описания 15.02.78

Гасударственный номитет

Совета ткиниотров СССР оо делам изобретений н открытий (5о) УД1 681.335.8 (088.8) (72) Авторы изобретения Л. Н. Костяшкин и П, B. Соловов (71) Заявитель

Рязанский радиотехнический институт (54) ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ

УСТ РОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано как в качестве автономного решающего узла, так и в качестве составной части частотно-импульсных вычислительных устройств.

Известно множительно-делительное устройство для частотно-импульсных сигналов (1 ).

Недостатком этого устройства являет ся появление динамической ошибки при измерении входных сигналов.

Известно также близкое по техническому решению к данному изобретению частотноимпульсное множительно-делительное устройство, (2 1 содержащее тритЧ.еры, эльменты И, дешифратор, первый вход которого соединен с единичным выходом первого триггера, а второй вход с единичным выходом второго триггера и первым входом первого элемента И, второй вход которого соединен с источником первой частоты, а выход является выходом устройства. IIepвый и второй выходы дешифратора соединены с первыми входами второго и третьего элементов И соответственно, вторые входы кото р ых соединен ы с исФочни ком второ и частоты, а выходы каждого из элементов

И соединены с нулевым и счетным входами первого и второго триггеров соответственно, Недостаток этого устройства в возникновении динамической ошибки, если одна из входных частот (или обе сразу) имеют во времени непродолжительные скачкообразные и зм ен ения.

1р Цель изобретения в снижении динамических погрешностей.

Это достигается тем, что в множительноделительное устройство введены: реверсивный счетчик, индикатор нуля, два элемен15 та И, элемент ИЛИ, элемент НЕ и блок анализа режима, первый и второй управляю щие входы которого подключены соответственно к источникам первой и второй частоты, выход соединен с суммирующим входом реверсивного счетчика и первым входом элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом индикатора нуля и входом элемента НЕ, а

25 второй вход — с первым входом пятого

596944

Устройство работает следующим образом.

В статическом режиме, когда отноше. ние частот Р1 и F во времени не изменяется, соцержимое реверсивного счетчика о

12 равно нулю, и элемент И 8 открьгг сигналом с выхода индикатора 13 нуля. Импульс частотной последовательности F проходит элемент И 8 и элемент HJIH 15 и устанавливает триггер 1 в состояние 1".

Дальнейшая работа устройства совпадает с прототипом; т.е. импульс частоты Н проходит открытый сигналом с цешифратора

4 элемент И 6 и устанавливает триггер 2 в состояние 1, при котором через открытый на время T> ф- элемент И 7 на выход

2 устройства проходят импульсы частоты Ю г элемента И и источником третьей частоты.

Второй вхоц пятого элемента И соединен с выходом элемента НЕ, а выход — с вы итаюшнм входом реверсивного счетЧика, нул .вые выходы каждого разряда которого соецинены со входами индикатора нуля.

Блок анализа режима содержит блок сравнения кодов, два . ÷åò èêà, два эле мента И, два формирователя импульсов и триггер, причем счетный вхоц триггера соединен с управляющим входом блока анализа, нулевой и единичные выходы — со Входами первого и второго формирователей, а, также с первыми входами первого и второго элементов И соответственно, вторь.е входы которых соединены со вторым управляющим входом блока анализа режима, а выходы со входами первого и второго. счетчиков соответственно, выходы первого и второго формирователей соединены со входами установки нуля первого и второго счетчиков соответственно, а выходы счетчиков — со входами блока сравнения кодов, выход которого является выходом блока анализа ,режима.

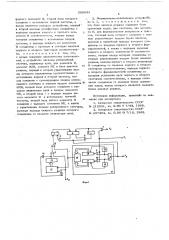

На фиг. 1 представлена блок-схема предлагаемого устройстве; на фиг. 2 — временные диаграммы, поясняющие принцип его работы.

Частотно-импульсное множительно-делительное устройство содержит триггер 1 с установочными входами; триггеры 2 и 3 со счетным входом, цешифратор 4 на два вхоца и два выхода, элементы И S. 6, 7, 8, 9, 10, 11 на два входа, реверсивный счетчик 12; индикатор 13 нуля; элемент

НЕ 14 элемент ИЛИ 15 íà цва входа; двоичные суммирующие счетчики 16, 17; формирователи 18, 19 импульсов; блок сравнения двоичных кодов 20; блок 21 анализа режима, Если импульсы частот F u F чере. дуются (т.е. + ==1), то выходнач час-тога Fq(t) = R(1).

При изменении отношения F+ / Р на выходе блока 2 1 анализа появляется импульс, который, пройдя элем н-, ИЛИ 15, установит триггер 1 в состояние 1 н, кроме того, запишет "1" в реверсивный счетчик 12, Так как содержимое реверсив10 ного счетчика уже не равно нулю, на выходе нндуктора 13 нуля исчезает сигнал, открывающий элемент И 8 и закрывающий через элемент НЕ 14 элемент Й 11. Импульсный сигнал с выхода блока 2 анализа, 1Б поступая HB установочный вход триггера 1, вызывает те же изменения в схеме, что и приход импульса частоты F, то есть на вьгхоце устройства формируется серия импульсов, число которых. равно F /F .

Если следующим за сигналом с блока 21 анализа придет импульс частоты F то

Ъ он нройцет только через открытый элемент

И 11, что изменит содержимое реверсивного счетчика 12 с ециницы на нуль, При .этом сигнал с индикатора 13 нуля откроет элемент совпадения И 8 и закроет через элемент HE 14 элемент И 11.

Иными словами, чтобы "опросить изменение сигналов F2, F с блока 21 анаЗ0 лиза поступает импульс, имитирующий импульс частоты F< . В то же время, чтобы не вносить этим действием погрешность в результат, следующий импульс частоты F

Ь не пропускается на установочный ахоп триг гера 1. На фиг. 2, на графике Р (t ) пунктиром показаны импульсы с блока 21 анализа, в котором в кажцом периоде определяется отношение F /F2 . В ) -том периоде частоты, когда триггер 3 стоит в

40 нуле, импульсы F> через элемент И 9 проходят в счетчик 16. В (j +1)-ом периоце частоты F в работе участвуют элемент

И 10 и счетчик 17. Блок 20 равнения

45 кодов сравнивает в момент прихода импульсов частоты Р2 содержимое счетчиков 16 и 17. Импульсы с. формирователей 18 и 19 импульсов производят обнуление счетчиков

16 и 17 перец новым счетом.

Использование предлагаемого устройства позволяет уменьшить динамические погрешности результата операции в случае непродолжительных скачкообразных изменений входной частоты F или F формула изобретени

Частотно-импульсное множительно- делительное устройство, содержащее триггеры, элементы И, дешифратор, первый вход которого соединен с единичным выходом первого триггера, второй вход — с единичным вь ходом второго триггера и первым входом

596944 цервого элемента И, второй вход которого соединен с источником первой частоты, а выход является выходом устройства, первый и второй выходы дешифратора соединены с первыми входами второго и третьего эле- 5 ментов И соответственно, вторые входы которых соединены с источником второй частоты, а выходы каждого из элементов

И соединены с нулевым и счетным входами первого и второго триггеров соответствен- 10 но, отличающееся тем, что, с целью снижения динамических погрешностей, в устройство введены реверсивный счетчик, индикатор нуля, два элемента И, элемент ИЛИ, элемент НЕ и блок анализа режима, первый и второй управляющие входы которого подключены соответственно к источникам первой и второй частоты, выход соединен с суммирующим входом реверсивного счетчика и первым входом элемента 2О

ИЛИ, второй вход которого соединен с вы- ходом индикатора нуля и входом элемента

НЕ, а второй вход — с первым входом пятого элемента И и источником третьей частоты, второй вход пятого элемента И соединен с выходом элемента HE, a выход с вычитаюшим входом реверсивного счетчика, .нулевые выходы каждого разряда которого соединены со входами индикатора нуля.

2. Множительно-делительное устройство по и. 1, о т л и ч а ю 1ц е е с я тем, что блок анализа режима содержит блок сравнения кодов, два счетчика, два элемента И, два формирователя импульсов и триггер, счетный вход которого соединен с первым управляющим входом блока анализа, нулевой и единичный выходы которого соединены со входами первого и второго формирователей, а также с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены со вторым управляющим входом блока анализа режима, выходы первого и второго элементов

И соединены со входами первого и второго счетчиков соответственно, выходы первого и второго формирователей соединены со входами установки нуля первого и второго счетчиков соответственно, а выходы счетчиков соединены со входами блока сравнения кодов, выход которого является выходом блока анализа режима.

Источники информации, принятйе во внимание при экспертизе:

1. Авторское свидетельство СССР

% 218531, кл. & 06 F 7/44, 1968.

2. Авторское свидетельство СССР

No 237464, кл. G 06 & 7/16, 1968, 596944 фиг. 2

Составитель А. Уткин

Редактор Трусов Техред З, мужик, - Корректор П. Небола

Заказ 1142/47 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений у ткрь тий

113035, Москва, Ж-35,.Раушскаи наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4