Устройство для микропрограммного управления

Иллюстрации

Показать всеРеферат

О П И С А Н И Е »isese4s

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 02.06.76 (21) 2367315/18-24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 05.03.78. Бюллетень № 9 (45) Дата опубликования описания 2S.Q2.78 (51) M. КЛ.2

G 06 Р 9/16

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325 (088.8 ) A. Г. Андрушенко, И. П. Барбаш, Г. Н.Тимонькин, С, Н. Ткаченко и Н. ф. фомин (72) Авторы изобретения (71) Заявитель (54) Ус пойство для мииропроГрдммного управления

Изобретение относится к области вычислительной техники и может быть использовано в различных ЦВМ.

Известно устройство для микропрограммного управления (1), содержащее запоминающее устройство, генератор тактовых импульсов, регистры, дешифраторы, блок распределения элементарных операций, блок переключения, вентили, элементы задержки и триггеры.

Недостаток устройства состоит в том, что оно требует больших затрат оборудования.

Наиболее близким к изобретению по технической сущности и достигаемому положительному результату является устройство <?I, содержащее матрицу внешних микрооперацнй, выход которой через матрицу внутренних микроопераций соединен со входом блока формирования адреса следующей микрокоманды, дешифратор, выход которого соединен со входом матрицы внешних микроопераций, первый и второй регистры микрокоманд, разрядные входы которых соединены с выходами элементов

И соответственно первой и второй групп, третью и четвертую группы элементов И, выходы которых соединены со входами дешифратора.

Информационные выходы блока формирования адреса следующей микрокоманды соединены с первыми входами элементов И первой и второй групп. Разрядные выходы первого и второго регистров микрокоманд соединены с первыми входами элементов И соответственно третьей и четвертой групп. Вторые входы элементов И первой группы соединены со вторыми входами элементов И четвертой группы. Вторые входы элементов И второй группы соединены со вторыми входами элементов И третьей группы.

Группа выходов матрицы внешних микроопераций соединена с выходами устройства.

Недостатками этого устройства являются сложность и низкое быстродействие.

Сложность устройства обусловлена тем, что для синхронизации работы используются два сложных тактовых генератора.

Низкое быстродействие устройства обусловлено. существованием ошибки рассогласования работы двух тактовых генераторов, которая равна промежутку от окончания тактового импульса одного тактового генератора до появления следующего тактового импульса от другого генератора. Длительность рабочего такта устройства должна быть не меньше времени последовательного прохождения сигнала пз nepBoãо (второго) регистра через выходные схемы

И, дешифратор, три матрицы, входные схемы

И и записи во второй (первый) регистр. Для достижения максимальной частоты работы в

596946

1О

25

35 о

S0

55 бо этом устройстве длительность тактового и мпульса должна быть равна длительности рабочего такта. Тогда максимальная частота работы устройства будет равна величине, обратной сумме значений удвоенной длительности тактового импульса и ошибки рассогласования двух тактовых генераторов. При заданной длительности рабочего такта предельная частота работы равна величине, обратной удвоенному значению длительности тактового импульса.

Однако достижение предельной частоты работы возможно лишь при скважности тактовых импульсов, равной двум. В известном устройстве достижение предельной частоты работы невозможно из-за ошибки рассогласования работы двуХ тактовых генераторов.

Цель изобретения — упрощение устройства и повышение его быстродействия.

Поставленная цель достигается тем, что предложенное устройство содержит триггер, единичный и нулевой, входы которого соединены с управляющими выходами блока формирования адреса следующей микрокоманды, а единичный и нулевой выходы — со вторыми входами элементов И первой и второй групп соответственно.

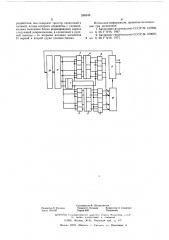

Структурная схема устройства представлена на чертеже.

Устройство микропрограммного управления содержит триггер 1, группы 2, 3 элементов И, регистры 4, 5 микрокоманд, группы 6, 7 элементов И, дешифратор 8, матрицу 9 внешних микроопераций, матрицу 10 внутренних микроопераций и блок 11 формирования адреса следующей микрокоманды.

На единичный вход триггера 1 с выхода блока 11 формирования адреса следующей микрокоманды поступает сигнал приэнака записи информации в регистр 5, на нулевой вход триггера 1 с выхода блока 11 поступает сигнал признака записи информации в регистр 4.

С единичного выхода триггера 1 на входы элементов И .группы 2 и элементов И группы

7 поступают тактовые импульсы первой последовательности, а с нулевого выхода триггера

1 на входы элементов И группы 3 и элементов

И группы 6 — тактовые импульсы второй последовательности.

Устройство работает следующим образом.

Триггер 1 установлен в единичное состояние. Сигнал с единичного выхода триггера

1 поступает на входы элементов И группы 2, а также на входы элементов И группы 7. В этом такте код выполняемой микрокоманды хранится в регистре 5, с выходов которого через открытые элементы И группы 7 код микрокоманды поступает на входы дешифратора 8. С выходов дешифратора 8 сигнал поступает на входы матрицы 9, которая формирует на своих выходах сигналы внешних микроопераций. С выходов матрицы 9 сигнал поступает через матрицу 10 внутренних микроопераций на входы блока 11 формирования адреса следующей микрокоманды. Блок 11 формирует код адреса следующей микрокоманды, который через открытые элементы И группы 2 записывается в регистр 4.

Одновременно на нулевой вход триггера 1 с выхода блока 11 поступает сигнал признака записи информации в регистр 4. По этому сигналу триггер 1 устанавливается в нулевое состояние. С нулевого выхода триггера 1 тактовый импульс второй последовательности поступает на входы элементов И группы 7, а также на входы элементов группы 3. Код микрокоманды, выполняемой в такте второй последовательности, хранится в регистре 4, куда он был записан по предыдущему тактовому импульсу первой последовательности. С выходов регистра 4 через элементы И группы 7 код микрокоманды поступает на входы дешифратора 8.

Далее через матрицы 9 и 10 сигнал поступает на входы блока 11, который формирует код адреса следующей микрокоманды. Этот код с выхода блока 11 через открытые элементы И группы 3 записывается в регистр 5. Одновременно на единичный вход триггера 1 с выхода блока

I1 поступает сигнал признака записи информации в регистр 5. По этому сигналу триггер

1 устанавливается в единичное состояние, и работа устройства повторяется в последовательности, описанной для такта первой последовательности.

Упрощение устройства обусловлено отказом от применения в нем двух тактовых генераторов. Повышение быстродействия достигается за счет получения с выходов триггера тактовых импульсов со скважностью, равной двум. При этом частота работы устройства равна предельной частоте и превышает максимальную рабочую частоту известных устройств.

Использование изобретения позволит упростить схемы и повысить быстродействие устройств управления UBM.

Формула изобретения

Устройство для микропрограммного управления, содержащее матрицу внешних микроопераций, выход которой через матрицу внутренних микроопераций соединен со входом блока формирования адреса следующей микрокоманды, дешифратор, выход которого соединен со входом матрицы внешних микроопераций, первый и второй регистры микрокоманд, разрядные входы которых соединены с выходами элементов И соответственно первой и второй групп, третью и четвертую группы элементов И, выходы которых соединены со входами дешифратора, причем информационные выходы блока формирования адреса следующей микрокоманды соединены с первыми входами элементов

И первой и второй групп, разрядные выходы первого и второго регистров микрокоманд соединены с первыми входами элементов И соответственно третьей и четвертой групп, вторые входы элементов И первой группы соединены со вторыми входами элементов И четвертой группы, вторые входы элементов И второй группы соединены со вторыми входами элементов

И третьеи группы, группа выходов матрицы внешних микроопераций соединена с выходами устройства, отличающееся тем, что, с целью упрощения устройства и повышения его быст596946

Составитель Ф. Шагиахметов

Техред О. Луговая Корректор А. Гриценко

Тираж 82б Подписное

Редактор Л. Утехина

Заказ П 41/47

ЦН И И П И Государственного комитета Соаета Министров . С I= по делам изобретений и открытий

1 l 3035, Москва, Ж-ЗБ, Рахивская наб., д. 4 о

Филиал ППП «Патент», г. Ужгород. ул. Проектная, 4

5 родействия, оно содержит триггер, единичный и нулевой, входы которого соединены с управляющими выходами блока формирования адреса следующей микрокоманды, а единичный и нулевой выходы — со вторыми входами элементов

И первой и второй групп соответственно. б

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР М 217О66, кл. G 06 F 9/16, 1967.

2. Авторское свидетельство СССР № 370607, а кл, G 06 F 9/16, 1971.