Устройство для обнаружения ошибок в контрольном оборудовании

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (11) 5969 фв

1 с (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.07.75 (21) 2153765/24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 05.03.78, Бюллетень ¹ 9 (45) Дата опубликования описания 25.02.78 (51) M. Кл.

5- 06 F 11/08

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.326.75 (088.8) (72) Авторы изобретения

Я. М. Лихтер и Н. A. Сирота (71) Заявитель

Киевский ордена Трудового Красного Знамени завод электронных вычислительных и управляющих машин (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В КОНТРОЛЬНОМ

ОБОРУДОВАНИИ

20

2;>

Изобретение относится к цифровым вычислительным машинам, оснащенным средствами оперативного контроля.

Известно устройство для обнаружения ошибок в контрольном оборудовании, содержащее триггеры, блок формирования контрольного разряда (1).

Недостаток этого устройства в ограниченном применении, так как оно может использоваться для контроля работы только комбинационных схем. Это устройство не обеспечивает полную проверку блоков контроля.

Известно также наиболее близкое по технической сущности к данному изобретению устройство для обнаружения ошибок в контрольном оборудовании, содержащее входной регистр, триггер контрольного разряда входного регистра, п регистров, п триггеров контрольного разряда, и триггеров управления, и блоков формирования контрольного разряда и блок выработки сигнала ошибки, причем входы входного регистра, триггера контрольного разряда входного регистра и триггеров управления являются входами устройства, выходы входного регистра соединены с соответствутощими входами и регистров и п блоков формирования контрольного разряда, выходы l1 блоков формирования контрольного разряда и выход триггера контрольного разряда входного регистра соединены со входами блока выработки сигHBла ошибки, выход которого является выходом устроиства, выходы и регистров и v. триггеров контрольного разряда являются выходами устройства и соединены со входами соответствующих контролируемых блоков, выходы которых являются выходами устройства (2).

Недостаток этого устройства в том, что на формирование информации с неправильными контрольными разрядами затрачивается много времени, сам процесс формирования не охвачен контроле», не реализуются все комбинации информации и контрольных разрядов (например, нулевой код информации с нулевым контрольным разрядо»). Кро»е того, это устройство не применимо в случае, когда информация из регистра, в котором она хранится с контрольным разрядом, пересылается ".о частям в несколько направлений и пересылки п1роизводятся с контроле».

Пель изобретения в повышении достоверности проверок блоков контроля.

Это дoc ièãài ТсН проверками блоков контроля в случае, когда производятся контролируем ыс пересь|лки отдельных порций информации из регистра в»есте с общим контрольным разрядом. Для чего в устройство введены триггер

596949 режима проверки, две группы элементов И и группа элpMентов ИЛИ, причем выход трипера контрольного разряда входного регистра соединен с первыми входами элементов И первой группы, выходы триггеров управления соединены со вторыми входами соответствуюших элементов И первой группы, единичный выход триггера режима проверки соединен с третьими входами элементов И первой группы, выхо3bI о 10KQB формирования контрольного разря (а соединены с первыми входами элементов И второй группы, вторые входы которых соединены с нулевым выходом триггера режима проверки, выходы элементов И первой и второй групп соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами соответствующих триггеров контрольного разряда.

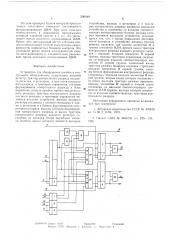

На чертеже изображена функциональная схема устройства. Рассмотрен случай, когда информация из регистра-ис-очника (входной регистр) пересылается в два регистра — приемника.

Устройство представляет собой часть цифровой вычислительной машины (ЦВМ), в которой производятся контролируемые передачи из регистра 1 и триггера 2 контрольного разряда входного регистра в регистры 3 и 4 с триггераv.è 5 и 6 контрольного разряда соответственно.

Для простоты изображения на чертеже показаны регистры. построенные íà динамических триггерах с общими стробами занесения.

Рабочий режим ЦВМ определяется нулевым состоянием триггера 7 режима проверки и триггеров 8 и 9 управления.

Работает l стройство следуюшим образом.

Информация с информационных входов

10 регистра 1 и входа 11 триггера 2 контрольного разряда входного регистра принимается в регистр 1 и триггер 2 по стробу 12 занесения.

Состояние регистра контролируется тремя блоками: олоком 13 формирования контрольного разряда для разрядов регистра 1, которые передаются в регистр 3; блоком 14 формирования контрольного разряда, для оставшихся разрядов регистра 1, которые передаются в регистр

4, блоком 15 выработки сигнала на выходе

16 ошибки контроля регистра 1 по сигналам от блоков 13 и 14 и от триггера 2 контрольного разряда входного регистра 1.

Блоки 13, 14 и 15 при контроле по нечетности представляют собой сумматоры по модулю 2. Как правило, каждый такой сумматор имеет два выхода — прямой и инверсный. На чертеже для простоты изображены только IlpBмые выходы.

При правильном приеме иа регистр 1 сигнал на выходе 16 имеет низкий уровень и соответствук)ший разряд регистра ошибок не будет устанавливаться в единичное состояние. Регистр ошибок на чертеже не показан.

При передачах с регистра 1 на регистры 3 и

4 вырабатываются стробы 17 и 18 занесения соответственно. Эти стробы могут выраоаты-. ваться одновременно и раздельно.

Для занесения в триггер 5 контрольного разряда регистра 3 в рабочем режиме выход блока 13 поступает I a первый вход элемента а

И 19. На второй вход элемента И !9 поступает сигнал с нулевого выхода триггера 7 режима проверки. Выход элемента И 19 поступает через элемент ИЛИ 20 на информационный вход триггера 5.

Выходы регистра 3 и триггера 5 поступают на контролируемый блок 2! и в другие цепи

ЦВЧ. Контролируемый блок проверяет сооТветствие информации в регистре 3 значению контрольного разряда в триггере 5 и, в случае выявления несоответствия, вырабатывает сигнал ошибки, который с выхода 22 поступает в регистр ошибок.

Занесение в триггер 6 контрольного разряда регистра 4 реализовано аналогично. Выход блока 14 поступает на первый вход элемента И 23.

На второй вход элемента И 23 поступает нулевой выход триггера режима проверки 7. Вь1ход элемента И 23 через элемент ИЛИ 24 поступает на информационный вход триггера 6. Контролируемый блок 25 вырабатывает на своем выхо е

26 сигнал ошибки при выявлении несоответст20 вия между содержимым регистра 4 и значением триггера 6. Сигнал с выхода 26 поступает на вход регистра ошибок.

В режиме проверки контролируемых блоков устанавЛиваются в единичное состояние триггер 7 режима проверки и триперы 8 и 9.

Установка этих триггеров производится пс отдельным управляющим сигналам (микрооперациям) на входы 27 и 28 в команде «Диагностика». На информационные входы 29, 30 и

31 триггеров 7, 8 и 9 поступает информация, 30 определяемая операндом этой команды. Триггеры 8 и 9 могут устанавливаться в единичное состояние одновременно или раздельно. Зти триггеры введены для осуществления раздельной проверки блоков 21 и 25. Раздельная провер35 ка контролируемых блоков упрощает разработку тестовых программ. Однако наличие триггеров 8 и 9 не является обязательным. Описание работы проводится для случая, когда оба трипера 8 и 9 установлены в единичное состояние.

В режиме проверки на нулевом выходе триггера 7 устанавливается низкий уровень, который заблокирует элементы И 19 и 23. На первый вход элемента И 32 поступает сигнал с выхода триггера 2. На второй вход элемента

И 32 поступает сигнал с единичного плеча триг4 гера 7. На. третий вход элемента И 32 поступает сигнал с выхода триггера 8. В зависимости от состояния триггера 2 устанавливается триггер 5. При приеме в регистр 3 информации, которая не соответствует значеншо триггера 5, î 1oK 2! вырабатывает сигнал ошибки, который с выхода 22 поступает в регистр ошибок и устанавливает в единичное состояние ссн>тветствуюгций разряд регистра ошибок. Состояние регистра ошибок может быть опрошено по специальной модификации команды «Диагностика». Таким образом устройство обеспс швает программную проверку блока 21.

Аналогичным образом производится проверка блока 25 через элемент И 33 и элемент

ИЛИ 24. Подбором кодов регистр» 1 можно произвесф полную проверку блоков 21,и 25.

596949

Форлула изобретения

ЦНИИП1! Заказ I!4ly47 Тираж 826 Подписное

Филиал П П П «Патент», г. Уж;орох. ", П роектпаа, 4

Полная проверка олоков контроля программными средствами повышает достоверность функционирования ICBM. При этом отпадает. необходимость в выполнении программного контроля (двойной Ilpoc÷åò и T. д.), что увеличивает время полезного использования HBM.

Кроме того, программный доступ к блокам контроля обеспечивает точную локализацию неисправностей, выявляемых блоками контроля. Это уменьшает время поиска неисправностей (время восстановления) и, следовательно, увеличивает время полезного использования ЦВМ.

Устройство для обнаружения ошибок в контрольном оборудовании, содержащее входной регистр, триггер контрольного разряда входного регистра, и регистров, и триггеров контрольного разряда, и триггеров управления, и блоков формирования контрольного разряда и блок выработки сигнала ошибки, причем входы входного регистра, триггера контрольного разряда входного регистра и триггеров управления являются входами устройства, выходы входного регистра соединены с соответствующими в одами и регистров и и блоков формирования контрольного разряда, выходы и блоков формирования контрольного разряда и выход триггера контрольного разряда входного регистра соединены со входами блока выработки сигнала ошибки, выхо:< которого является выходом

17 устройства, выходы п регистров и и триггеров контрольного разряда являются выходами устройства и соединены со входами соответствующих контролируемых блоков, выходы которых являются выходами устройства, отличающееся тем, что, с целью повышения достоверности контроля в устройство введены триггер режима проверки, две группы элементов И и группа элементов ИЛИ, причем выход триггера контрольного разряда входного регистра соединен с первыми входами элементов И первой группы, выходы триггеров управления соединены со вторыми входами соответствующих элементов И первой группы, единичный выход триггера режима проверки соединен с третьими входами элементов И первой группы, выхо1s ды блоков формирования контрольного разряда соединены с первыми входами элементов И второй группы, вторые входы которых соединены с нулевым выходом триггера режима проверки, выходы элементов И первой и второй групп соединены со входами соответствующих эле20 ментов ИЛИ группы, выходы которой соединены со входами соответствующих триггеров контрольного разряда.

Источники информации, принятые во вниманис при экспертизе:

l. Авторское свидетельство СССР № 470810 кл. G 06 F !1/04, 1973.

2. Патент США № 3465132, кл. 235- 153, ! 968.