Устройство для решения систем дифференциальных уравнений

Иллюстрации

Показать всеРеферат

Окблиз; .-,:

О П И C А Й Й Е щаэбэв",.

ИЗОБРЕТЕИЙЯ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свнд-ву (22) Заявлено 28.04.75{21) 212S042i18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.03.78. Бюллетень № 9 (45) Дата опубликования описания 15.02.78 (51) М. Кл

& 06 Р 15/32

Государственный комитет

Воввте Мнинстрао СИР по делам изобретений и открытий (53) УДК 681.325

{ 088. 8) (72) Авторы и а обретен и,в

П. Боюн, Л. Г. Козлов и Б. Н. Малиновский (71) Заявитель

Ордена Ленина институт кибернетики АН Украинской ССР

{ 54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИ ЕМ

ДИФФЕPEl(UHAЛЪНЫХ УРАВНЕНИЙ

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интегрирую них машин и однородных вычислительных структур, предназначенных для решения систем обыкйовенных дифференциальных уравнений.

Известно устройство для решения сис- тем дифференциальных уравнений, содержащее интеграторы и блоки умножения (1).

Однако известное устройство не может быть использовано при решении систем уравнений высокого порядка из-за большого объема оборудования.

Наиболее близким техническим решением 1а к данному предложению является цифровое интегрирующее устройство для решения систем обыкновенных дифференциальных урав- нений матричным способом, содержащее интеграторы, матрицу блоков умножения, при- щв чем выход каждого интегратора. соединен с первыми входами блоков умножения соответствующей строки матрицы, первые входы блоков умножения последней строки матрицы соединены со входами устройства (21.

Однако это известное устройство отличается большим объемом оборудования, так как для решения систем уравнений т -ro порядка устройство содержит тт многовходовых сумматоров и (в + 2 ) ° n сложных блоков умножения, кроме того, оно дает большие погрешности, поскольку в блоках умножения содержатся остатки, которые в сумме могут,.представлять большие величины нри высоком порядке решаемой системы уравнений.

Целью изобретения является упрощение устройства и повышение точности.

Для этого блоки умножения каждого столбца соединены последовательно, выход каждого из блоков умножения последней строки соединен с входом соответствующего интегратора и вторыми входами соответствующих блоков умножения первой строки матрицы, причем блок умножения содержит регистр, преобразователь кода, первый вход которого соединен с выходом регистра, второй вход является первым входом блока умножения, одноразрядный сумматор, первый вход которого соединен с вторым входом

3 блока умножения, второй вход соединен с выходом преобразователя кода, третий вход— с выходом элемента запоминания переноса, влад которого соединен с выходом одноразрядного сумматора, выход которого сое-

5 динен с входом элемента запоминания суммы, выход которого является выходом блока умножения.

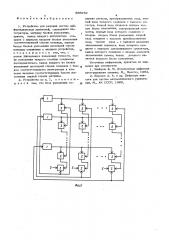

Иа фиг. 1 приведена структурная электрическая схема устройства, на фиг. 2 — 1О структурная электрическая схема блока умножения.

Устройство для решения систем дифферен- циальных уравнений содержит и интеграторов 1 и (1ъ+ 1) ° g блоков умножения 2. j5

Выхоцы каждого из е интеграторов

1 соединены с первыми входами н блоков умножения 2 в каждой из д, строк матрицы соответственно, (lan+1) блоков умножения 2. в каждом столбце матрицы соединены пос- 20 ледовательно, а выход (n+1)-ro в столбце блока умножения 2 соединен с вторым вхо-, дом первого в столбце блока умножения 2 и с входом соответствующего интегратора 1.

Входы 3 устройства соединены с первыми >25 входами блоков умножения 2(Ът +1)-й стро- ки, Блок умножения 2 содержит одноразрядный сумматор 4 (см. фиг. 2), элементы запоминания переноса 5 и суммы 6, преобразователь 7 кодов и регистр 8. Блок умножения 2 имеет входы 9 и 10 и выход11.

Первые входы 10 блоков умножения 2 в каждой строке соединены между собой и подключены к выходам соответствующих интеграторов 1. Выходы ll,каждого предыдущего в столбце блока умножения 2 соединены с вторыми входами 9 каждого последующего в столбце блока умножения 2, 40

Выход 11 (за+1)-го. в столбце блока ум« ножения 2 соединен с вторым входом 9 первого в столбце блока умножения 2 и входом соответствующего интегратора 1.

Устройство работает следующим об45 разом.

В регистрах 8 л блоков умножения 2 устанавливаются значения коэффициентов ц ц, а в регистры 8 блоков умножения

2 (т+1)-й строки заносятся коды величины

Si.. На первые входы 10 блоков умноже-, ния 2 (p +l)-N строки подаются приращения функции 6 (, а на первые входы 10 блоков умножения 2 с первой по L -ю строку поступают приращения, от с вы ходов интеграторов 1.

В первом такте осуществляется выдача первого младшего разряда коэффициентов

d:.„ и остатков Ь„: на предыдущей

L ° 1

60 итерации на одноразрядные сумм;тары 4

4 блока умножения 2 первой строки, в которых. вычисляются величины (S + d.a > 1 )1 3.

На К -м такге выдается .К -й разряд к к коэффициентов Q.ö и остатков Ь„на одноразрядные сумматоры 4 блока умножения 2 первой строки, т.е. (4 -ттт+1)-й разряд коэффициентов .Ф на одиара зряд; ные сумматоры 4 блока умножения 2 щ-й строки, =1, 2 ... К:. После (и+1)-го такта на выходы блоков умножения 2 (@ +1)-й строки выдается младшия разряд величины g и „ Ы +. Ь Й f"

И

В результате работы устройства на послецуюших р тактах (р — разрядность) вычисляются все р разрядов правой части системы уравнений и запоттинаются на элементах запоминания суммы 6. Затем с выходов блоков умножения 2 (tl +1)-й строки разряды переполнения поступают на входы соответствуюптих интеграторов 1, в которых осуществляется оцерапия интегрирования и вырабатываются новые значения переполнения

Предыдущие итерации осуществляются аналогично вышеизложенному, причем значения правых частей, вычисленные на предыдущей итерации и зафиксированные на элементах запоминания суммы б, используются на последующей итеграции, поступая младшими разрядами вперед на входы блоков умножения 2 первой строки.

В зависимости от соотношений разряд ности р и порядка и решаемой системы уравнений (1) столбцы блоков умножения

2 могут разбиваться на К(К= Г ) параллельных идентичных цепей последовательно соединенных блоков умножения 2 по:р блоков в каждой цепи, Такое разбиа ние позволяет повысить быстродействие устройства, Технико-экономический эффект настоящего предложения состоит в томр что даннОе устройство имеет меньший объем,оборудова« ния по сравнению с известными устройствами, так как из известного устройства исключены е. сложных многовходовых сумматоров, а з -разрядные регистры (a +1) ° чт блоков умножения 2 замены одноразрядными элементами запоминания суммы б. Кроме того, данное изобретение позволяет повысить точность решения задачи, поскольку вычисление правой части в предлагаемом устройстве осуществляется с погрешностью младшего разряда (2 а в известных устройствах с погрешностью

2 . Это достигнуто путем исключения

TL остатков в регистрах блоков умножения 2 и заменой нх одним суммарным

-разрядным остатком, 5 формула изобретении

5969

1. Устройство для решения систем дифференциальных уравнений, содержащее ин-, теграторы, матрицу блоков умножения,, причем, выход каждого интегратора соединен с первыми входами блоков умножения соответствующей строки матрицы, первые входы блоков умножения последней строки матрицы соединены с входами устройства, о т л и а ю щ е е с я тем, что, с целью упрощения и повышения точности, блоки умножения каждого столбца соединены последовательно, выход каждого из блоков умножения последней строки соединен с вхо- дом соответствующего интегратора и вторыми входами соответствующих блоков ум- . ножения первой строки матрицы.

2. Устройство по и. 1, о т л и ч а ющ е е с я тем, что блок умножения со52

6 держит регистр, преобразователь кода, первый вход которого соединен с выходом ре.гистра, второй вход является первым входом блока умножения, одноразрядный сумматор, первый вход которого соединен с вторым входом блока умножения, второй вход соединен с выходом преобразователя кода, третий,вход — с выходом элемента запоминания переноса, вход которого соединен с выходом одноразрядного сумматора, выход которого соединен с входом элемента запоминания суммы, выход которого яв- ляется выходом блока умножения, Источники информации, принятые во внимание при экспертизе:

1. Майоров ф. М. Электронные цифровые интегрирующие машины, М., Машгиз, 1962, 2. Воронов А. A. и др. Цифровые аналоги для систем автоматического управления, М.. АН СССР, 1960, .596952

Составитель В. Тарасов

Редактор А. Зиньковский Техред 3. фанта Корректор Л. Небола, Заказ 1142/47 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„д. 4/5 филиал ППП Патент, г. Ужгород, ул, Проектная, 4