Преобразователь полярных координат вектора в прямоугольные

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (" 596955 (61) Дополнительное к авт. свид-ву— (22) Заявлено 19.02.76(21) 2326985/18-2 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 05.03.78. Бюллетень № 9 (45) Дата опубликования описания 25.02.78 (51) М. Кл.

& 06 Р 15/34

Государственный комитет

Совета Иинистроа СССР оо делам изобретений и открытий (53) УДК 681.325 (088. 8) (72) Авторы изобретения

B. Н. Соломаха, А. Г. Шевяков и А, И. Сдвижков (71) Заявитель

Рязанский радиотехнический институт (54) ПРЕОБРАЗОВАТЕЛЬ ПОЛЯРНЫХ КООРДИНАТ ВЕКТОРА

В ПРЯМОУГОЛЬНЫЕ

Предложенное устройство относится к автоматике и вычислительной технике и может быть использовано в качестве автономного устройства для преобразования координат либо в составе вычислителя при решении различного рода специальных задач.

Известно частотно-импульсное тригонометрическое устройство для вычисления тригонометрических функций, содержащее блок определения интервалов, датчики образцовых частот, логическое триггерное кольцо, следящие системы, блок выдачи результатов (11. Однако в нем значительны аппаратурные затраты, обусловленные выбранным способом формирования линейного участка функции, в соответствии с которым на каждый интервал аппроксимации требуется хранить два параметра; жесткие требования к пульсации входной частоты, моделирующей модуль вектора, и ее диапазону, связанные с использованием в устройстве частотно-импульсных следящих систем.

Наиболее близким по технической сущности к изобретению является преобразователь полярных координат вектора в прямоугольные (21, содержащий формирователь стробов, два элемента И, элемент ИЛИ, коммутатор, два делителя, первый триггер, блок памяти и переключатель квадрантов, а формирователь стробов содержит счетчик и третий элемент И, причем первые входы первого и второго элементов И подключены соответственно к первому и второму выходам блока памяти, а выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента

ИЛИ, единичный выход первого триггера подключен к первому входу блока памяти и первому входу коммутатора, а нулевой выход первого триггера подключен ко вторым входам блока памяти и коммутатора, группа управляющих входов коммутатора подключена к выходам переключателя квадрантов, а выходы коммутатора соединены со входами соотвеT<òíóþùèõ делителей. Однако данный прототип имеет сравнительно небольшой диапазон изменения входной частоты, что обусловлено принятым способом реализации, требуемой при интерполяции операции умножения с помощью двоичного умножителя.

Целью изобретения является расширение диапазона входных сигналов.

Для этого введены в блок формирования стробы второго и третьего триггера и узла сравнения, причем выход элемента ИЛИ соединен с третьим входом коммутатора, а нулевой выход первого триггера подключен к единичному входу второго триггера, нулевые входы вто596955

5 о

Формула" изобретения

50 рого и третьего триггеров соединены с единичным входом первого триггера, нулевой выход второго триггера подключен к входу третьего элемента И, выход которого соединен со входом счетчика, управляющий выход которого подключен к нулевому входу третьего триггера, а группа выходов — к группе входов узла сравнения, выход которого соединен с единичным входом третьего триггера, нулевой и единичный выходы которого подключены соответственно ко вторым входам первого и второго элементов И.

Су щность изобретения поясняется чертежами.

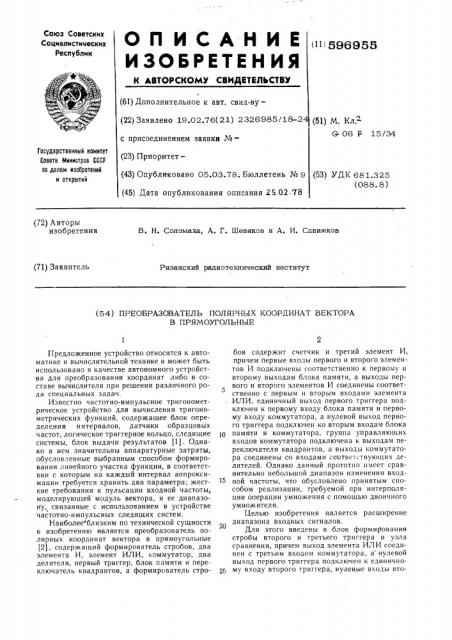

На фиг. 1 приведена структурная электрическая схема устройства, содержащего формирователь стробов 1, первый и второй элементы

И 2 и 3, элемент ИЛИ 4, коммутатор 5, два делителя 6 и 7, первый триггер 8, блок памяти

9 ii переключатель квадрантов 10.

На фиг. 2 приведена структурная электрическая схема формирователя стробов, поясняющая принцип формирования интервалов, пропорциональных интерполирующим множителям, содержащая второй и третий триггеры 11 и

12, узел сравнения 13, счетчик 14 и третий элемент И 15.

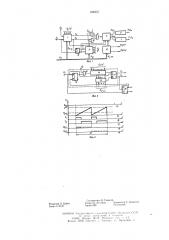

На фиг. 3 приведены временные диаграммы.

С приходом каждого импульса входной частоты F,- в блоке 1 организуется два цикла формирования интервалов г и г. Триггер 12, срабатывающий по импульсу F,, разрешает прохождение частоты F> на вход счетчика 14.

С этого момента на его импульсных выходах начинают формироваться опорные частотные составляющие F>/2", а на потенциальных выходах чо времени развертывается линейно изменяюц;ийся код N„. максимальное значение которого равно 2 (m — разрядность счетчика

14)

Интервалы r i и г, формируются на выходах триггера 11 путем сравнения линейно растущего кода N«H B iHoio Ko NT т, . Единичное состояние три repa 14, стробирующего выходные частоты блока памяти, изменяется импульсом из узла сравнения, появляющимся в момент N„=N>» затем восстанавливается импульсом переполнения.

Триггер 8 позволяет организовать два цикла формирования т1 и . > и управляет коммутацией частот с выхода блока памяти 9 с целью получения (N„ ) и (N ),- последовательно во времени. Г1о второму импульсу переполнения счетчика 14 устанавливается в исходное состояние триггер 8 и сбрасывается триггер 12. Работа преобразователя на этом прекращается до появления следующего импульса F - .

Предложенный принцип реализации операции умножения позволил исключить в схеме

45 преобразователя блок умножения, что уменьшило в два раза время, необходимое для формирования число-импульсных кодов (N )х и (NT. ), т. е. увеличить в 2 раза диапазон изменения входной частоты.

Расширение диапазона входных cm палов позволяет уменьшить общее количество используемых преобразователей при тех же аппаратурных затратах на каждый из них, а следовательно, сократить стоимость всего устройства в целом.

Преобразователь полярных координат вектора в прямоугольные, содержащий формирователь стробов, два элемента И, элемент ИЛИ, коммутатор, два делителя, первый триггер, блок памяти и переключатель квадрантов, а формирователь стробов содержит счетчик и третий элемент И, причем первые входы первого и второго элементов И подключены соответственно к первому и второму выходам блока памяти, а выходы первого и второго элементов

И соединены соответственно с первым и вторым входами элемента ИЛИ, единичный выход первого триггера подключен к первому входу блока памяти и первому входу коммутатора, а нулевой выход первого триггера подключен ко вторым входам блока памяти и коммутатора, группа управляющих входов коммутатора подключена к выходам переключателя квадрантов, а выходы коммутатора соединены со входами соответствующих делителей, отличающийся тем, что, с целью расширения диапазона входных сигналов, в блок. формирования стробов введены второй и третий триггеры и узел сравнения, причем выход элемента ИЛИ соединен с третьим входом коммутатора, а нулевой выход первого триггера подключен к единичному входу второго триггера, нулевые входы второго и третьего триггеров соединены с единичным входом первого триггера, нулевой выход второго триггера подключен к входу третьего элемента

И, выход которого соединен со входом счетчика, управляющий выход которого подключен к нулевому входу третьего триггера, а группа выходов — к группе входов узла сравнения, выход которого соединен с единичным входом третьего триггера, нулевой и единичный выходы которого подключены соответственно ко вторым входам первого и второго элементов И.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 389517, кл. G 06 F 15/34, 12.07.71.

2. Авторское свидетельство СССР № 463986, кл. G 06 F 15/34, 07.11.74.

596955

Фик t

Фиг.3

Редактор Л. Бабич

Заказ I I 4 i (47

Ш1ИИ11И Госуда, твен и к игета Совет; Ми«.и .рои СССР по делам изобр. ний и о г, рь.-. ии

I 13035. Москвы. Ж-, 1, ). Расгцская иы<ь. л. 4 Б

Филиал Г!Г1П «Патент>;, г. Ужгоро к x,ë. !!!ни KTH;1R, 4 (NF) x (ц ) Составитель В. Тарасов

Текред О. Луговая Корректор Л. Гриценко

Тираж 826 Подписное