Вычмслительное устройство

Иллюстрации

Показать всеРеферат

Союз Соаетскик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву— (22) Заявлено 15.07.75(21)2156491/24 (11) 596964

1 (51) М. Кл2

G 06 Q 7/12 с присоединением заявки № тоеударстеекный камктет

Сееата Меестраа СССР, аа делам аеааретеинй к открытий (23) Приоритет (43) Опубликовано 05.03.78.Бюллетень №9 (53) УДК 681.335. .5 (088.8) (45) Дата опубликования описания 24.02.78

М. В. Джанелидзе, Г. Б. Чхеидзе, Е. И. Рабинович, Г. Н. Габашвили и Р. И. Кахидзе (Т2) Авторы изобретения

Тбилисский филиал Всесоюзного научно-исследовательского института метрологии им. Д. И. Менделеева (71) Заявитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Йзобретение относится к области вычислительной и измерительной техники.

Известны вычислительные устройства, в которых с целью выполнения множитепьноделительных операций над многими входными сигналами используются посйтедовательно-параллельно соединенные множитепьно-делительиые блоки.

Одно из известных устройств содержит .обший импульсный трансформатор, первичная обмотка которого воспринимает выходные импульсы временного модулятора, а вторичные обмотки управляют ключевыми триодами амплитудных модуляторов и в том числе амплитудного модулятора, входящего в состав временного модулятора. Каждый из амплитудных модуляторов содержит ключевой триод, выходной делитель напряжения и выходной резисторно-емкостной фильтр.

Другое известное устройство содержит два компаратора, два входа первого из которых и один вход второго соединены с источниками входных сигналов, и фильтр, выход которого соединен со вторым входом второго компаратора. Кроме того, устройство содержит фиксатор напряжения, входы которого соединены с выходами компараторов, а вь ход подключен ко входу фильтра..

Известно также наиболее близкое по тех5 ннческой е -шности к данному изобретению

° вычислительное устройство, содержащее нечетное число множитепьно-делительных блоков, пара информационных входов каждого из которых является входами устройства, крощо ме цоследнего множительно-депитепьного блока, в I котором один из информационных входов является выходом устройства, управляющий выход каждого нечетного множительно-целительного блока, кроме последнего, р соединен с первыми управляющими входами собственного и последуюшего четного. множитепьно-делительного блока, управпяюший выход каждого четного множительно-делительного блока соединен со вторыми уп2О равляюшими входами собственного и последуюшего нечетного множитепьно-делительного блока, а управляюший вход последнего множитепьна-делитепьного блока соединен с собственным первым управляющим входом, И с вторым управпяюшим входом первого.мно596964 жительно-делительного блока и с выходом устройства.

Основными недостатками указанных иэвестньгх устройств являются низкая точность, надежность и технологичность, обусловленные зависимостью разброса параметров weментов, их характеристик и коэффициента передачи от изменения температуры.

Цель изобретения в повышении точности, гехнологичности и надежности устройства за счет термокомпенсации при больших управляющих сигналах, температурной стабиливации коэффициентов передачи управляемых проводимостей, их характерисгик и разброса параметров элементов при изменении температур.

Это достигается тем, что каждый множи I тельно-делительный блок содержит термокомпенсируюшяе и резистивные элементы и эле- 20 менты с управляемой проводимостью, ñoåдиненные в два термореэистивных моста, связанных общим терморезистивным плечом, два линейных преобразователя, выходы которых связаны с управляющим входом со-

25 ответствующего элемента с управляемой проводимостью, параллельно каждому из которых включен термокомпенсируюший элемент, а также усилитель и компаратор, входы кото30 рого соединены с первыми выводами элементов с управляемой проводимостью, включенными в одно иэ плеч соответствующего терморезистивного моста, вторые выводы элементов с управляемой проводимостью, 35 вывод общего термореэистивного плеча и один вывод диагонали каждого терморезистивного моста, соединены с шиной нулевого потенциала, другие выводы диагоналей терморезистивных мостов соединены с информационными входами .множительно-делительного блока, выход компаратора через усилитель связан с управляющим выходом множительноделительного блока, а входы линейных преобразователей подключены соответственно к первому и второму управляющим входам множительно-делительного блока.

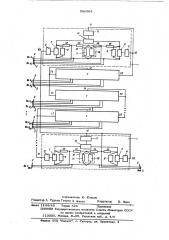

На чертеже представлена принципиальная схема выЧислительного устройства, выполненная согласно данному изобретению.

Устройство содержит множительно-делительные блоки„1, информационные входы 2 устройства, выход 3 устройства, линейные прео разователи 4, 5, элементы 6, 7 с управляемой проводимостью, термокомпенсирую- шие элементы 8, 9, компаратор 10, усилитель 11, реэистивные элементы 12, 13, 14, 15, терморезистивное плечо 16, содержащее резистор 17 и терморезистор 18, управляющий выход 19 множительно-делительного блока, первый 20 и второй 21 уп1 равляющие г:ходы множительно-делительного блока.

Работает устройство следующим образом.

Все множительно-делительные блоки 1 образованы двумя терморезистивными мостами, причем последний множительно-делительный блок 1 отличается от всех предыдушнх способом формирования компенсационных сигналов.

В множительно-делительных блоках 1, кроме последнего, формирование компенсационного сигнала осуществляется соединением управляющего выхода 19 через линейный преобразователь 4 к входу элемента 6 с управляемой проводимостью, которому параллельно подключен термокомпенсирующий элемент 8. Один иэ выходов элемента с управляемой проводимостью 6 подключен к первому входу компаратора 10, ко второму входу которого присоединен один из выходов элемента с управляемой проводимостью 7, параллельно зашунтированного .термокомпенсируюшим элементом 9. Под действием входных сигналов Х и У, подключенных к входам 2 устройства и управляющих сигналов e(,8) S (81), вырабатываемых элементами с управляемой проводимостью 6 и 7, условие компенсации примет вид, 80(8„)3 Тй(t )Ц ST(8 1 Т (t,)х,() <

Из выражения (1) следует, что всякое изменение входных информационных переменных А,g, Ь (8) вызывает разбаланс множительно-делительных блоков 1. При этом, компенсационная цепь вырабатывает управляющий сигнал З, который, воздействуя на элементы 6, 7 с управляемой проводимостью, приводит множительна-делительС ные блоки 1 в равновесное состояние.

И последнем множительно-делительном блоке 1 управляющий выход 19 соединен через линейный преобразователь 4 с элемен том управляемой проводимости 6 и соединен с выводом диагонали выходного терморезистивного моста; общая точка резисторов 14, 15, к которому подключен выход 3 устройства. Такое соединение позволяет реализовать компенсатор выходного сигнала элементом с управляемой проводимостью 7, т.е.

Вк (8„,„)Г„ "3Ы „„1 = ) Ae .E — выходной сигнал.

Параллельное включение термокомпенсируюшнх элементов 8, 9 и терморезистора 18 соответственно к элементам с управляемой проводимостью 6, 7 и резистору 17 обеспечивает термокомпенсацию и термостабилизацию положения рабочей точки и снижение

596964

5 впияния разброса параметров в диапазоне изменения температуры и оценивается коэффициентом температу-раап. . нестабипьности.

Т(;Р) EI .III f (ЬЗЧ, бает 4с)a 1, где . 4 Ц z — изменение выходного тока

Ч элементов с управляемой проводимостью при постоянных jjpoBHRK входных информационных сигнапов в диапазоне температур.

Е, йТ вЂ” температурное смешение иход(о ной характеристики элементов с управпяемой проводимостью.

b — изменение коэффициента передачи между терморезистивными спаренными мостами в диапазоне температур.

При воздействии на множительно-делительные блоки 1 входных информационных сигH&B0B К 1 К яп+ g У1.. Я< И Управляю»

ШИХ СИГН&ПЫ 91,,.9 „,1,9,,.. &Яiа1 CO1 гласно условию (1, ) цопучим систему:

20 уравнений вида:

®®6Ж <5;)>,= (1)r, ;) "1 ° е Ед % е(< ) а"®ч®з)4 Фк)"а

° O ° °

° . ° ° .. ° ., м ° а ГЪ1

s6 (61@) А Ta(tзп) 4

= S ®апаше а<, )" ® )4 в а -И

=ЬЧ (6у,1)Ц 19 211ю)хр,+„ где 5 Щ1)...6<(Q,> )к 31(Я;)... Ь (9, ) регупируемые коэффициенты. йередачи эпемен тов 6 и 7 с управляемой проводимостью при воздействии на них управпяюших сигна1 t

81... 1,. и е 1 6,„.„

f < — коэффициенты передачи пиней1> ных пдеобразоватепей. те 1 )a фЬ ф11 1f и тц Щ, тЯ f Ó 1) 4о

Вычислительное устройство, содержащее нечетное число мнэжитепьно-депитепьных блоков. пара информационных входов каждого из KDTopbEK является входами устройства, кроме пэспеднегэ миэжитепьнэ-делительного блока, в котором один из информационных входов является выходом устройства, управпяюший выход каждого нечетного множитепьно-депитепьнэго блока, кроме поспеднегэ, соединен с первыми управпяюшими входами собственнэгэ . -.эспедующего четного множитепьнэ-депнтепьнэго блока, управпяюший выход каждого четного мнджитепьно-депитепьнэгэ блока соединен со вторыми управпяюшими входами собственного и поспедующего нечетного множитепьно-депитепьного блока, а управляюший вход пэспеднего л1ножитепьно-делительного блока соединей с собственным первым управпяюшим входом, с вторым управляю- щим входом 1первor э мнэжитепьно-целительного бпока и с выходом устройства, о т— пичаюшееся тем, что, спепьюнэвышения точности, технологичности и надежности устройства, в нем каждый множительно-депитепьный блок содержит термокомпенсируюшне и резистивные элементы и элементы с управляемой прэвэдиллэстью, соединенные в два терморезистивных моста, сцязанных общим термэрезнстивным плечом, два линейных преэбразэвателя, выходы котов рых связаны с управляющим входом соответствующего элемента с управляемой проводимостью, параллельно каждому из которых включен термокэмпенсируюший элемент, а также усилитель и компаратэр, входы кэ» торого соединены с первыми выводами эЖменментов с управляемой проводимостью, вкпюченными в одно з плеч соогветствуюшегэ термэрезистивнэгэ моста, вторые выводы элементов с управпяел1эй прэвэдил1эстью, вывод эбшегэ термэрезистизногэ плеча и один вывод диагонапи каждого терморезистивного моста соединены с шиной нупевэгэ потенпиапа, другие выводы диагоналей термэрезистивных мостов соединены с информационными входами мнэжитепьнэ-депитепьного блэка, выход компаратэра через усипитепь связан с управпяющим выходом мнэжитепьно-депитепьнэгэ блока, а входы линей ных преобразоватепей подключены сэответственнэ к первому и второму управпяющнм входам множитепьно-депитепьнэго блока. (4

0 1 1

55 коэффициенты температурной нестабипьности.

Принимая во внимание, что в множительно-депитепьных блоках 1 коэффициенты передачи Ь(8) эпементов 6 и 7 с управпяемой ирэвэдимэстью идентичны и, решая систему (3) относительно Ь, где выходной сигнал окончательно получим:

Ц5 g(t 1) g{,tg). Tg(t „) T (t )к хх„.х бо ч " и() >II(<2).. кЬ;„)Тя(t „.1).3 у, у„ конструктивная постоянная, Таким образом, данное вычиспитепьное устройство осушествпяет множитепьнв-делитепьные операции со многими вводными сиг66 папами и обладает повышенной точчостью работы, технопогичнэстью и высокой надежа остью.

Фoðìула изэбретення

596964

Составитель Ю. Козлов

Редактор Г. ТрусощТехред 3, и анти KDpp8xTDp Е, Папп

Заказ 1144/48 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/6

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4