Устройство для интегрирования

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

И АВТОРСКОМУ СВИДИВЛЬСТВУ

Союз Советских

Социалистических

Республик

ОЙ» 596966 (И) Донолнительиое к.авт. саид-ну(22) Заявлена19.01.76.t21)2316020/18-24 (б1) М. Кл.

G 06 9 7/18 с,присоединением заявки № (23) ПриоритетГаауяаратввнны» «аивтвт

Саввта Мнн«атрва СССР ав диан вввбрвтвнвв а втнрылй (43) Опубликовано0,5.03.78. Бюллетень ¹g (53) УДК 681.335 (088.8) (45) Дата опубликования описания 23.02,78 (72) Автори изобретения

М. Н, лазов и З. С. Никулин

\ (73) Заявитель (84) УСТРОЙСТВО ДЛЯ ИНТРГРИРОВАНИЯ

Изобретение относится к автоматике я вычислительной технике н предназначено для Формирования напряжения IIposopwoseëü ного интегралу от входного сигнала. Оно может спользоваться В системах автоматн" ческого управления различных технологичны ских процессов и. объектов, когда требуются боль|иие постоянные интегрирования.

Известны устройства для интегрирования, содержашие реверсивные спетчики импульсов, аифро-аналоговые преобразователи и преобразователи напряжение - частота, выполненные на основе аналоговых интеграторов и компараторов (1) .

Однако в известных устройствах вслед-- ц ствие сбоев счетчика под действием случайных цомех и перерывов в подаче питания происходит разрушение информации, накопленной интегратором, что может приводить к аварийным последствиям, а потому N во многих случаях совершенно, недопустимо.

Указаний недостаток устраняется в аналого-цифровом интеграторе с контуром для восстановления информации, содержащем трехпоэиционный блок сравнения, последо- И вательно соединенные аналоговый интегратор, компаратор, реверсивный счетчик импульсов, цифро-аналоговый преобразователь, выход которого подключен к первому входу сумматора, источник задания начальных условий и источник управляюшего сигнала, блок управления, один вход которого соединен с выходом сумматора, а другой - с источником управляюшего сигнала (2) .

Однако этОт интегратop отличается слож костью схемы, требуюшей применения в контуре восстановления информации трехпоэиционного блока сравнения, низким быстро действием в режимах записи начальньпс угловий и восстановления информации, что цри сбоях счетчика может приводить к возникновению значительной погрешности интегратора иэ-за разряда эапоминакицего конденсатора в блоке слежения - хранения. В конечном счете снижается надежность и то .ность интегратора.

Целью изобретения является повышение надежности и точности устройства.

Для этого оно содержит .дополнительный аналоговый интегратор и клюж причем вы596966

3 ход сумматора соединен ; через первый ключ с входом аналогового интегратора, и через второй ключ — с входом дополнительного аналогового интегратора, выход которого соединен с вторым входом сумматора, третий вход сумматора через третий ключ соединен с источником задания на ;альных условий,. источник управляющего сигнала соединен с управляющим входом третьего ключа и входом установки счетчика.в нулевое поло- 0 f жение, а выходы блэка управления соединены с управляющими входами первого .и второго ключей и с управляющим входом аналогового интегратора.

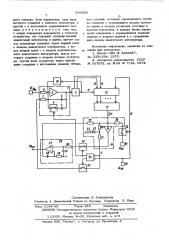

На чертеже приведена структурная элек- 13 трическая схема устройства.

Устройство для интегрирования содержит аналоговый интегратор 1, построенный на операционном усилителе 2, в цепь обратной связи которого включены кищеисаторы 3 ®0 и 4, соединенные параллельно через ключ

5; ° íà входе усилителя 2 включены резисторы 6 и 7, к первому из которых подсоединен источник входного сигнала 8 У „°

Выход усилителя 2 подключен к компаратору 9, обеспечивающему сброс аналогового интегратора в начальное положение через цепь обратной связи 10. Импульсный выход компаратора подсоединен к счетному входу 11 реверсивного счетчика импульсов 12. Р

Входы управления реверсом (сложением и вычитанием) 13 и 14 счетчика 12 соединены с потенциальными выходами компаратора

9, а цепь 15 установки нуля счетчика 12 подключена к источнику 16 управляющего сигнала (. нц ) °

Выходы счетчика 12 подключены к сетке резисторов цифро-аналогового преобразова40 теля 17; соединенного с первым входом сумматора 18, построенного на операционном усилителе 1 9.

Усилитель 19 охвачен нелинейной отрицательной обратной связью, образованной

45 двумя последовательно включенными резисторами,20 и 21, точка соединения которых через встречно включенные стабилитрэны

22 и 23 подключена K корпусу устройства.

Выход сумматора 18 через ключ 24 соединен с входом аналогового интегратора 1 и через второй ключ 25 — с неинвертирующим входом дополнительного аналогового интегратора 26, включающего в себя операционный усилитель 27 с конденсатором 28

55 в цепи отрицательной1 обратной связи, резистор 29 и апериодическое звено (резистор 30 Ф конденсатор 3 1) .

Выход дополнительного аналогового интегратора 26 подключен к второму входу

60 сумматора 18, к третьему входу которого

4 через ключ 32 подключен источник задания начальных условий 33 (Q ).

Сумматор 18 подключен йепосредственно к входу блока управления 34, соединенного цо выходам с управляющими входами ключей 5, 24 и 25. Другой вход блока управления 34 подключен к источнику управляющего сигнала 16 (нц ).

Для рассматриваемого устройства харак терны следующие режимы работы: интегрирование; восстановление информации и запись начальных условий.

В режиме интегрирования сигнал Ьи О, ключ 32 разомкнут, и блок управления 34 находится в состоянии, при котором ключи

5 и 25 замкнуты, а ключ 24 разомкнут.

При наличии входного сигнала (U Ф О) аналоговый интегратор 1 интегрирует этот сигнал, и на вход компаратора поступают импульсы с частотой, пропорциональноф Оц„.

При этом в зависимости от знака Ug, на потенциальных выходах компаратора 9, соединенных с входами управления реверсом13 и 14 счетчика 12, устанавливаются напряжения, настраивающие счетчик на сложение или вычитание .импульсов.

Возникновение импульсов на счетном ахо» де 11 реверсивного счетчика импульсов 12 происходит в моменты времени, когда напряжение на выходе усилителя 2 достигнет, уров ня срабатывания компаратора 9, после чего под действием цепи обратной связи 10 осуществляется быстрый сброс аналогового интегратора (разряд. включенных параллельно конденсаторов 3 и 4). В результате.компаратор 9 выключается, и процесс интегрирования (заряда конденсаторов 3 и 4). под действием напряжения у,„ повторяется. С помощью компаратора 9 в счетчике 12 фиксируются величина и знак приращения интег рала входного напряжения Uf,q, т.е. осуществляется квантование интеграла входного сигнала по уровню.

Преобразование цифрового кода N. „характеризующего интеграл |Up сИ., в элекФ Ъ трическэе напряжение 0 „(выходной сигнал интегратора) осуществляется с помопц ю цифро-аналогового преобразователя 17, сумматора 18 и дополнительного аналогового интегратора 26.

При надлежащем выборе постоянной интегрирования 1 ц дополнительного аналогового интегратора 26 и постоянной. времени С апериодического звена (30и 31) в режиме, когда ключ 25 замкнут, интегра тор 26 благодаря отрицательной обратной связи через сумматор 18 успевает следить за током l> на выходе цифро-аналогоаого преобразователя 17 так, что динамическая ошибка на выходе сумматора 18 близ-

596966 ка к нулю. Поэтому стабилитроны 22 и

23 находятся в непроводяшем состоянии, и сумматор 18 работает на линейном участ«е своей статической характеристики.

В установившемся режиме, хранения интеграла при 0 „ =О напряжение ),„ „="К

LM=, 8JUg .clt, где R -сопротивление резистора 35.

Если по каким-либо причинам в процессе интегрирования Ьигнала Q о или хра- 10 юх

1 пения интеграла произойдет сбой счетчика

12 и прирашенне напряжения на выходе сумматора 18 превысит допустимое значение, то стабилитроны 22 и 23 откроются. Из-эа выключения отрицательной обратной связи сумматор 18 переходит в состояние цоложительного или отрицательного насышения и вызывает срабатывание блока управления

34. Под действием этого блока ключи 5 и

25 размыкаются а ключ 24 замыкается 20

Благодаря этому конденсатор 4 отключается, выходной сигнал U сумматора

18 через ключ 24 поступает на форсируюший вход аналогового интегратора 1, а дополнительный аналоговый интегратор 26 переходит в режим хранения предшествуюшего сбою значения Ug щ.

В результате под действием сигнала Ц при условии - р ЪЬ ф- где Яб и 9Л

U.

Ме сопротивления резисторов 6 и 7, восстанм ливается информация в счетчике 12, так как подача,,импульсов на счетный вход 11 счетчика 12 осушествляется до тех пор, пока напряжение ц не снизится до величины Оп, при которой произойдет выключение блока управления 34. После этого ключ 24 размыкается, Ключи 5 и 25 замыкаются, и устройство возврашавтся в исходное состояние, обеспечивая дальнейшее формирование интеграла от входного сигнала Ug

Из-за отличия Un от нуля после сбои. счетчика 12 и возврашения устройства в ис4! ходнов состояние происходит изменение напряжения Ug » на величину ЬЦ ь - к

Цд где к = — -. — — коэффициент усиления

В2 + R21 %. сумматора 18, причем 120, 21 и КЬ5— сопротивления резисторов 20, 21 и 35 со1 ответственно.

При К » 1, что обычно легко выполняется на практике, погрешность, связанная с налячием о, может быть сделана достаточно малой. Другая сэставляюшая погрешности, обусловленная изменением ц, 55 из-за разряда конденсаторов 28 и 31 дополнительно аналогового интегратора 26 в режиме восстановления (при разомкнутом ключе 25), может бьггь уменьшена за счет

6( снижения времени восстановления, В рассматриваемом устройстве этэ время,сушественнэ меньше, чем в известны» благодаря тому, что в режиме восстанов ления частота работы интегратора 1 может бьггь увеличена на несколько порядков за счет отключения конденсатора 4 СЗ С4, где СЗ и С4 — емкости конденсаторов 3 и 4.

Рассмотрим теперь работу устройства в режиме записи начальных. условий (Ь ц 1) . В этом случае счетчик 12 устанавливается в нулевое состояние и на аход сумматора

18 через замкнутый ключ 32 подается напряжение начальных условий Ун, Одновременно под действием сигнала Лиц блок управления 34 переводит. ключи 5 и 25 в замкнутое состояние, а ключ 24 - в разомкнутое. Благодаря отрицательной обратной связи через сумматор 1Ь на выходе дополнительного аналогового .интегратора 26 устанавливается.напряжение начальных условий, определяемое соотношением Царях ЕФ Ц

Зб (1 =0), где К 35 и В 36 - сопротивления резисторов 35 и 36 соответственно. После того, как сигнал нц примет нулевое значение, происходит размыкание ключа 32 и сигнал U отключается от сумматора 18. В результате на выходе сум-матора 18 возникает скачок напряжения выэываюший срабатывание блока управления 34 подобно тому, как это происходит в режиме восстановления информации.

Блок управления 34 размыкает ключи

5 и 25, .замыкает ключ 24 и код M в .счетчике 12 изменяется до значения Яо, соответствуюшего заданной величине напряжения. Qg»„.о-, после чего происходит выключение блока управления 34 и устройство переходит в режим интегрирования входного сигнала

Таким образом, благодаря указанным выше конструктивным признакам достигается упрошение интегратора и повышение его быстродействия в режимах восстановления информации и †.писк начальных условий, что в конечном счете приводит к повышению надежности и точнэсти устройства.

Формула изобретения

Устройство для иьтегрирэвания, содержашее пэследэвате п-.нэ соединенные аналоговый интегратор, кэмпаратэр, реверсивный счетчик импульсов, цифро-аналоговый преобразователь, выход которого пэдключен к первому входу сумматора, источник задания начальных условий и источник управляю596966

Составитель Л. Снимщикова

Редактор А. Зиньковский Техред О. Луговая Корректор Е. Папп

Заказ 1144/48 Тираж 826 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

mего сигнала, блок управления, один вход которого соединен с выходом сумматора, а другой - c источником управляющего car нала, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и точности устройства, оно содержит дополнительный аналоговый интегратор и ключи, причем выход сумматора соединен через первый ключ с входом аналогового интегратора, и через. второй ключ - с входом дополнительного аналою ового интегратора, выход коTop0Fo соединен с вторым входом сумматора, третий вход сумматора через третий ключ соединен с источником. задания началь

8 ньяи условйй,. источник управляющего сигнала соединен с управляющим входом третьего ключа и входом установки счетчика в нулевое положение, а выходы блока управления соединены с управляющими входами первого и второго ключей и с управляющим входом аналогового интегратора.

Источники информации, принятые во внимание при экспертизе:

1. Патент США % 3288627, кл. 235-194, 1975.

2. Авторское свидетельство СССР

И 507872, кл. 906 Ф 7/18, 1974.