Приемное устройство для измерения характеристик группового времени запаздывания в каналах связи

Иллюстрации

Показать всеРеферат

Ф(1 та1" яотин м

ОПИС Е.

ИЗОБРЕТЕНИЯ

Соаоз Советским

Социалистическим

Республик (11) 597992

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к ввт. свид-ву т (51) М. Кл. (ф 01 В 27/28 (И} Заявлено .1 10275 (21) 2107388/21 с присоединением заявки М (23} Приоритет

Геврдервтвеииыи иевитат еаввта Мвиеотрав OOOO ие иолов иооаретавий и отирмтеа (43) Опубликовано 150 78.Бтоллетеиь ph 10 (53) УДК 621.317.742 (088. 8) (45} Дата опубликования описания 170278 (72) ВтоРЫ изобретения Г.П. Черный, В.В. Цытрон, В.Г. Бондаренко и В.Г. Шевченко (71) Заявитель (54) ПРИЕМНОЕ VCTPOACTBQ ДЛЯ ИЗМЕРЕНИЯ

ХАРАК1ЕРИС1ИК ГРУППОВОГО ВРЕМЕНИ ЗАПАЗДЫВАНИЯ

В КАНАЛАХ СВЯЗИ

Изобретение относится к области измерительной техники связи и может быть использовано для измерения и регистрации относительной частотной характеристики ГВЗ в каналах связи на фиксированных частотах.

В настоящее время для решения задачи измерения характеристики группового времени запаздывания используют. устройства, основанные на передаче по испытуемому объекту модуI лированных сигналов с дискретными значениями частот. измерительных несущих, чередующихся со средней несущей частотой и сравнении на приеме фаз между огибающими этих сигналов.

Известно устройство, содержащее устройство выделения испытательных сигналов, узел задержки, блок управления, кварцевый генератор импульсов с делителем частоты, блок измерения и,индикации(1,(.

Устройство имеет погрешности измерения из-эа качания фронтов сигнала, влияния флюктуационных помех.

Прототипом изобретения является устройство, содержащее узел выделения испытательных сигналов, кварцевый генератор импульсов и блок управления, один иэ сбросовых выходов кой торого подключен к сбросовому входу распределителя, а другой — к сбросовым входам двух фазоэапоминающих делителей частоты, к выходам которых подключен блок измерения и индикации, соединенный с блоком управления(2).

Это устройство также имеет погрешности, обусловленные влиянием флюктуационных помех и.качанием фрон10 тов сигнала на выходе усилителя-ограничителя.

Целью изобретения является повышение точности измерения.

Цель достигается тем, что в усття ройство.для измерения характеристики группового времени запаздывания в каналах связи, содержащее узел выделения испытательных сигналов на входе, кварцевый генератор импульсов и тИ) блок управления, один из сбросовых выходов которого подключен к сбросовому входу распределителя, а другой к сбросовым входам двух фаэоэа" поминающих делителей частоты, к вы25 ходам которых подключен блок измерения и индикации, соединенныйс блоком управления, введены блок фазирования, биполярный преобразователь фазы, выходы которого через последовательно

ЗО соединенные запирающие элементы И, 597992

При поступлении на вхо," приемного устройства посылки опорного сигнала все схемы дискретных узлов устройства сигналом сброс 1 yñòàíàâëèваются в исходное состояние.

В устройстве 3 из напряжения огибающей формируются импульсы прямоугольной формы. С выхода устройства 3 эти импульсы поступают одновреО менно на измерительный вход биполя н ого преобразователя фазы и через р" суммирующий элемент ИЛИ 4 на вход распределителя.

Через время равное Т щ (где 1 о

15 ло период огибающей, 2 — целое число) на первом выходе распределителя 5 появляется сигнал разрешение иэмеt ° рения, который открывает запирающие элементы И 7, 8 и запускает

И к блок 2. В результате на выходе бл— ока 2 появляются прямоугольные имсов пульсы, фаза которых приблизитель но впадает с фазой опорного сигнала на выходе устройства 3. Эти импульсы поступают на опорный вход биполярQ5 ного преобразователя 6 и суммирующий элемент ИЛИ 4. Длительность импульсов на выходе суммирующего элемента ИЛИ 4 зависит от Фазового сдвига менду импульсами иа выходах устройЭО ства 3 и блока 2 и равна временному интервалу между передним фронтом опережающего и задним фронтом отстающего импульсов. Эадний Фронт этих импульсов соответствует концу одного измерения. делители усреднения, с просовые входы которых объединены со сбросовым входом распределителя, и коммутатор знака суммирования подключены ко входам фаэозапоминающих делителей частоты, другие входы ко;орых сбединены с выходом запускающего элемента И причем к выходам узла выделения испытательных сигналов и блока фазирования параллельно подключены входы биполярного преобразователя фазы и через суммирующий элемент ИЛИ— счетный вход распределителя, один из выходов которого соединен с фазирующим входом блока фаэирования и разрешающими входами запирающих элементов И, запрещающие входы которых подключены ко второму выходу распределителя и входу разрешающего элемента И, выход кварцевого генератора импульсов соединен с импульсными входами блока фазирования, запирающих элементов И и запускающего элемента И

1 другой вход которого соединен с выходом Разрешающего элемента И и синхронизирующим входом блока измерения и индикации, при этом вход блока управления подключен к входным зажимам устройства, синхронизирующий выход подключен к входу разрешающего элемента И и управляющему входу коммутатора знака суммирования, а сбросовый вход блока фазирования объединен со сбросовыми входами фазозапоминающих делителей частоты.

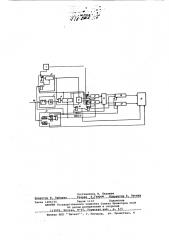

На чертеже представлена функциональная схема устройства.

Устройство содержит кварцевый генератор 1 импульсов, блок 2 фазирования, устройство 3 выделения испытательных сигналов, суммирующий эле мент ИЛИ 4, распределитель 5, биполярный преобразователь 6 фазы, запирающие элементы И 7, 8, делители 9 и 10 усреднения, коммутатор 11 знака суммирования, фазозапоминающие делители 12, 13, разрешающий 14 и запускающий 15 элементы И, счетноиндикаторный блок 16, блок 17 управления.

Устройство работает следующим образом. 60

После прохожденья по каналу связи испытательный AN-сигнал поступает на вход устройства 3 выделения испытательных сигналов и блок 17 управления, в котором вырабатываются сигналы БВ наличия посылки опорного или измерительного сигнала, сигнал сброс 1, совпадающий по времени с началом посылки опорного сигнала, и сброс 2 совпадающий по времени с началом Ю посылки измерительного или опорного сигнала. Эти сигналы необходимы для получения соответствующего алгоритма обработки фазы огибающей испытательных сигналов.

На суммйрующем и вычитающем выходах биполярного преобразователя фазы 6 появляются иьщульсы, разность длительностей которых равйа удвоенному временному. сдвигу. между входными сигналами. Подсчет числа измерений осуществляется при помощи распределителя 5. Через и .измерений на втором выходе распределителя появляется сигнал конец измерений, которым закрываются запирающие элементы И 7

8.

I 1 аким образом на выходах биполярноГо преобразователя фазы появляются две серии импульсов, суммарная разность длительностей которых равна t *22 И;, (=1 где at < — временной сдвиг между сигналами на входах биполярного преобразователя 6 при поступлении на вход устройства посылки опорного сигнала.

Полученные на выходах преобразователя 6 сигналы при помощи запирающих,. элементов И 7, 8 заполняются высокочастотными импульсами, поступающими с выхода кварцевого генератора 1.

Образованные пакеты импульсов поступают далее на соответствующие делите597992

Х аФ -g, ь 4 х 1 I ср ли 9, 10 с коэффициентом деления равным 2 и.

Если на вход устройства поступает посылка опорного сигнала, то импульсы с выхода делителя 9 через коммутатор 11 поступают на вход фазозапоминающего делителя 12, а с выхода делителя 10 через коммутатор 11 — на вход фазоэапоминающего делителя 13.

Таким образом, разность между числами записанными в фазозапоминанхцие делители 12 и 13 равна и и .е

i-t u где 1 р — чатота высокочастотных импульсов кварцевого генератора 1.

При поступлении на вход приемного устройства посылки измерительного сигнала в блоке 17 формируются сигналы измерительная посылка и сброс 2 . Последний, все схемы, кроме блока 2 и делителей 12, 13, сбрасывает s исходное состояние. Фаза сигнала на выходе блока 2 фаэирования остается. такой же, как и при посылке спорного сигнала.

Процесс сравнения фаз сигйалов на вьйсодах блока фазирования 2. и устройства 3 аналогичен случаю поступления иа вход устройства посьн.ки опорного сигнала. При этом сигнал с делителя 9 записывается в фаэоэапоминающий делитель 13, а сигнал с делителя 10 .— в фазозапойииаквций делитель 12, tIps одновременном появлении сигналов запрет измерения и измерительная посылка íà вЫход г разрешающего элемента И. 14. появляется сигнал разрешения запуска фазозапоминающих делителей, который открывает запускающий элемент И 15..Б ре зультате высокочастотные импульсы через элемент H 15 поступают одновременно на входы фазоэапоминающих делителей 12, 13. На выходах этих делителей появляются прямоугольные импульсы, сдвинутые по времени относительно друг друга на величину, равную среднему значению измеряемой неравномерности группового времени запаздывания в где 1; — временной сдвиг между сигналами на выходах устройства 3 и бло-, ка 2 при поступлении измерительного сигнала на вход устройства.

Временной сдвиг между сигналами на выходах фазозапоминающих делителей 12, 13 измеряется в счетно-индикаторном блоке 16. Сброс предыдущих показаний осуществляется передним фронтом сигl0 !

26 йв

35.

40 нала, разрешающего запуск фазоэапоминающих делителей.

Формула изобретения

Приемное устройство для измерения характеристик группового времени запаздывания в каналах связи, содержащее узел выделения испытательных сигналов на входе, кварцевый генератор импульсов и блок управления, один из сбросовых выходов которого подключен к сбросовому входу распределителя, а другой — к сбросовым входам двух фаэозапоминающих делителей частоты, к выходам которых подключен блок измерения и индикации, соединенный с блоком управления, о .т л и ч а ющ е е с я тем, что, с целью повышения точности измерения, в него введены блок фазирования, биполярный преобразователь фазы, выходы которого через последовательно соединенные запирающие элементы И, делители усреднения, сбросовые входы которых объединены со сбросовым входом распределителя, и коммутатор знака суммирования подключены ко входам фазозапоминающих делителей частоты, другие входы которых соединены с выходом запускающего элемента И, причем к выходам узла выделения:исйытательных сигналов и блока фазирования подключены входы биполярного преобразователя фазы и через суммирующий элемент ИЛИ вЂ” счетный вход распределителя, один из выходов которого соединен с фазирующим вхо дом блока .фазирования и разрешающими входами запирающих элементов И, запрещающие входы .которых подключены ко второму выходу распределителя и входу разрешающего элемента И, выход кварцевого генератора импульсов соединен с импульснь|4и входами блока фазирования, запирающих элементов И и запускающего элемента И, другой вход которого соединен с выходом разрешающего элемента И и синхронизирующим входом .блока измерения и индикации; при этом вход блока управления подключен к входным зажимам устройства, синхронизирующий выход подключен к входу разрешающего элемента И и управляющему входу коммутатора знака суммирования, а сбросовый вход блока фаэирования объединен со сбросовыми входами фазоэапоминающих делителей частоты.

Источники информации, принятые во внимание при экспертизе:

1. Техническое описание измерителя затухания и времени запаздывания

П-323 И 383 2Г 1.400000ТО.

2. Авторское свидетельство СССР

9 428309, кл. $.01 Ц, 27/28, 1 72

Составитель Н. Ледащев

«Ревактор Н. Зайцева Техред К.Гаврон Коооектор А. Лакида

Заказ 1209/35 Тираж 1112 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4/5

Филиал ППП- Патент, г. Ужгород, ул. Проектная, 4