Устройство для сопряжения

Иллюстрации

Показать всеРеферат

ОП ИСА Е

ИЗОБРЕТЕНИЯ

Союз Советскин

Социалистимескин

Республик (ц)598064

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свнд-ву (22) Заявлено 26.07.76 (21) 2394386/18-24 о (51) M. Кл.

С1 06 V 3/04 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.03.78Бюллетень № 10 (45) Дата опубликования описания 22.04 78

Гасударственный комитет

Саавтв Министров СССР аа делам изооретений н открытий (53) УДК681.327 (088.8) А. А. Пыжов, А. В. Беланович, В. В. Салогуб, А. Ф. Толочко и М. E Макаренко (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СОПРЯ)КЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано при сопряжении двух синхронных систем передачи дан ных (СПД) ре альн эго м асш таба вр емени. 5

Известно устройств о для с опряжения дискретного канала связи с ЭВМ, содержащее регистр сдвига, соединенный с процессором и через буферный блок — с внешними устройствами, регистр управляющего слова, соединенный с процессором, регистром связи и буферным блоком, блок адресоа соединенный с процессором и регистром управляющего слова, дополнительный регистр управляющего слова, блэк модификации адре- 15 сов и блок анализа, причем дополнительный регистр управляющего слова соединен с процессором, блоком. анализа и через блэк модификации адресов — с блоком адресов, а блок анализа - с регистром связи и блоком мэ- 20 дификации адресов (1). Однако ограниченные функциональные воэможности известного устройства не позволяют обеспечивать сопряжение синхронно работающих быстродействующих устройств, Наиболее близким 25 к изобретению пэ технической сущности является устройство для сопряжения, содержащее буферный блок памяти и блок зашиты

or ошибок, первые вхэды которых соединены со входом устройства, блок преобразова-. ния кодов, соединенный выходом с первым входом блэка формирования кэдограммы, первый выход которого подключен к выходу усгрэйства, и блок управления, соединенный входом с первым выходом блока защиты

or ошибок, а первым выходом-со вторым входом блока формирования кодограммы, выход буферного блока памяти и второй выход блока управления подключены к соот ветствуюшим входам блока преобразования кодов (2 .

Целью изобретения является упрощение схемы. B описываемом устройстве это дос тигается тем, что в него введен блэк фикса»

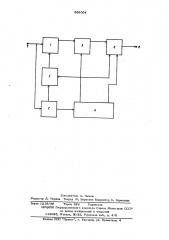

LiHH режима, выпэлненнЫй в виде триггера, два входа которого соединены соответственно со втэрыми выходами блока зашиты эт ошибок и блока формирования кэдограммы, а выход подключен кэ второму входу буферного блока памяти, На чертеже приведена блок-схема описываемого устройстве

Оно содержит буферный блок 1 памяти, блок 2 зашиты от ошибок, блок 3 фиксации режима, блок 4 управления, блок 5 пре образования кодов, блок 6 формирования ко« дограммы, вход 7 и выход 8 устройства.

Информация, поступающая на вход 7 ус1 ройства, записывается в буферный блок 1 памяти и одновременно поступает для 1О контроля на блок 2 зашиты or ошибок. В случае, если сообщение принято без ошибки, то блок 2 зашиты от ошибок формирует сигнал "Правильно", по которому блок 3 фиксации режима блокирует поступление 13 информации на входе устройства на время, определяемое длиной информационных кодо вых комбинаций и скоростью приемной(и передающей СПД. При етом по сигналу из блока 4 управления организуется переза пись информации иэ буферного блока 1 памяти в блок 5. преобразования кодов, из которого по сигналу блока 4 управления переписывается в блок 6 формирования кодограммы, где формируется сообщение соответствующего формата, предназначенное для последовательной передачи на выход устройства. При этом блок 6 формирования кодограммы в соответствующий мо» мент выдает сигнал Сброс", по которому и у 3! блок 3 фиксации режима снимает блокировку входной информации. B случае, если сообщение принято с ошибкой, то бпок 2 защиты от ошибок формирует сигнал "Ошибка", 3 по которому блок 3 фиксации режима не блокирует информацию на входе и устройство принимает следующее сообщение. Ошибочное сообщение не обрабатывается и не нередае тся.

Таким образом, описываемое устройство позволяет обеспечивать сопряжение двух рази отипных синхронных систем передачи данных.

Ф ормула изобретения

Устройство для сопряжения, содержащее буферный блок памяти и блок зашиты or ошибок, первые входы которых соединены со входом устрсйства, блок преобразования кодов, соединенный выходом с первым входом блока формирования кодограммы, первый выход которого подключен к выходу устройства, и блок управления, соединенный входом с первым выходом блока защиты от ошибок, а первым выходом-со Вторым входом блока формирования; 1кодограммы, выход буферного бпока памяти и второй выход блока управления подключены к соответствующим входам блока преобразования кодов, о т л и ч а ю ш е е с я тем, что, с целью упрощения устройства, в него введен блок фиксации режима, выполненный в виде триггера, два входа которого соединены соответственно со вторыми выходами блока зашиты от ошибок и блока формирования кодограммы, а выход подключен ко второму входу буферного блока памяти.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

¹ 404088, кл. Q 06 7 9/19, 1970, 2. Гойхман Э. Ш. и Лосев IQ И. Передача информации в автоматизированных системах управления, М„Связь, 1971.

50SM4

Составитель А. Пыжов

Редактор Л. Тюрина Техред М. Борисова Корректор С. Гарасиняк

Заказ 1219/39 Тираж 826 Подписное

ПНИ ИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филнал ППП Патент, r. Ужгород, ул. Проектная, 4