Устройство вычисления функций

Иллюстрации

Показать всеРеферат

L

3 b

Союз Советских

Социалистических

Республик

Ю59807О (6!) Дополнительное к авт. свил-ву (22) Заявлено 03,11,75(2 I) 2186053/18-24 с присоединением заявки № (» 0g Р 7/3Ц 0183p!,TB!!H!! Й KOцфиаяя11 к ртг !;икр (23) Приоритет (43) Опубликовa!íî 1 5.03. 7&.- Бюллетень И. = 0- (53)

I (45) QBTB опубликования описанн-"" 7-02.7 »

УД1(СЕ! 325 5

{! Я С5) (72) Авторы н обретрнии

Q,ß;, )Êä6ð,! ß !.I К- ппейч к, g, Я., ;",-.карев

/ и В И, Тарасенко

{7j) Заявитель

Киевский ордена Ленина политехнический институт имени 50-летия Великой Октябрьской соцпалис ической революции

{ 54) УСТРОИСТВО BbI ×CÕÐ" II I H л- УНКЦ1 1И

Изобретение относится к области вычислительной техники и может быть применено в цифровых вычислительных машинах, пост роенпых на интегральных схемах.

Известны устройства вычисления функций, представляющие собой табличпые вычислители, построенные на основе блока постоянпой памяти Щ . Однако эти устройства имеют ограниченные функциональные возможности.

Н8260Me близким техническим решешпэм {j к данному изобретению является устройство вычисления функций содержащее регистр сдвига, группа выходов которого соединена с группой входов входного регистра, соединенного своими выходами с блоком памяти 15 и выходной регистр (21.

Это устройство также имеет ограниченные функциональные возможности. С его помощью нельзя вычислять функции в неавтономном режиме, когда операнд посту- 20

Г пает на вход устройства поразрядно и ф-я цифра результата формируется раньше поступления (+1)-й цифры операнда в устройстве. Это не позволяет эффективно использовать такое устройство в системах 25 управления пропессамн в реальном масштабе времени, когда информация поступает на вход устройства в последовательном коде со старших разрядов, Кроме того, в этом устройстве не может быть сокращено число внешних выводов без существенного уменьшения его производительности. Прн вычислении функции необходимо, чтобы операнд был представлен и двоичными разрядами, В этом случае в устройстве необходимо наличие большого числа внешних выводов, которое увеличивается с увеличением разрядности представления операнда и результата. Это затрудняет его реализацию в виде большой интегральной схемы. белью изобретения является расширение функциональных возможностей.

Это достигается тем, что предлагаемое устройство дополнительно содержит коммутатор, блок сравнения кодов и лемент И, первый вход которого является входом устройства, выход соединен с управляющим входом входного регистра, группа выходов регистра сдвига соединена с первой группой входов коммутатора, вторая группа

598070

3 входов которого соединена с группой выходов блока памяти, группа выходов коммутатора соединена с первой руппой входов блока сравнения кодов н с группой входов выходного регистра, группа выходов которого соединена со второй группой входов блока сравнения кодов, первый и второй выходы блока сравнения кодов являются соответствующими выходами усзройства, при атом второй sxoa элемента И, управпяккцие l0 входы регистре сдвига, выходного регистра и блока сравнения кодов являются соответс1 венно первым, вторым, третьим и четвер тым управпжошыми входами устройства.

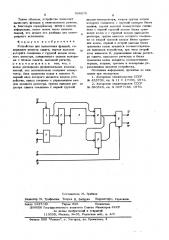

Яа чертеже изображена структурнай схА д ма предлагаемого устройства.

Устройство содержит регистр сдвига 1, входной регистр 2, блок памяти 3, коммутатор 4 выходной регистр 5, блок сравнения кодов 6 и элемент И 7. Регистры 1,2,5 20 содержат К разрядов, гаа П разрядность, представления операнда и.результата. Ком мутатор 4 может быть построен, например, в виде треугольной матрицы, состоящей иэ и -строк элементов И. Каждая 1 -я строка

25 атой матрицы содержит -i элементов И. К одним входам элементов И 4 -го столбца матрицы подкаючен:i -й выход блока памяти 3. Ко вторым входам элементов И кажЖ дой бтрокыцодключея." j - и (Ъ регистра сдвига 1. llaw разделения по выходам апементов И одного столбца можно использовать апементв ИЛИ. Входной регистр

2 можно построить на основе М-S òðèããåðoâ.

Тогда при вычислении монотонно возрастаЫшых функций выходы регистра сдвига 1 подключены к R-входам триггеров входного регистра 2, а пры вычислении монотонно убывающих функций - к 8 входам входног6 0 регистра 2.

Устройство предназначено для вычисления в неавтономном режиме непрерывных монотонно:убываккцых ипи возрастающих функ-4 ций, величина производной которых в области определения не превышает по модулю .

@3ынымы. Например яю sill х и Q = @os x при Оах З4ых пры ++2 =(а+их) пры х 4 21, у f и других. 50

Устройство работает следующим образом.

При вычислении монотонно возрастающей функции и исходном состоянны во всех разрядах входного регистра 2 записаны едини-, цы, а пры.вычислении монотонно убывающей

55 функции - нули. Независимо от вида вычисляемой функции выходной регистр 5 установлен в нулевое состояние, ав старшем раз .Г ряде регистра сдвига 1 записана единица.

В блоке памяти 3 записана таблица функции.

I в заданном интервале. Ипя вычисления фучкции выполняется ц цикпов, состоящих из четырех тактов. К началу каждого j -ro цикла на информационный вход 8 поступает инверсное значение 1 -го разряда исходного операнда (операнд поступает, начиная со старших разрядов). Яа управпяющие входы 9-12 в каждом такте поспедоватепьно во времени поступают управляющие сигналы.

В.,первом такте по управляющему сигналу, п.ступающему на управляоший вход 9, откпьь веется элемент И 7 и инверсное значение очередного разряда операнда управляет приемом кода входного регистра 2. Если оче- редной разряд операнда равен нулю, что соответствует единичному информационному сигналу, то,1- и разряд входного регистра

2 меняет свор состояние на противоположное. Формируется новое входное слово во входном регистре 2 и бпок памяти 3 выдает на входы коммутатора 4 выходное cnoso соответствующее этому входному слову.

Прн этом на выходах коммутатора 4 в каж« дом 4-ом цикле присутствует код, состоящяй ыэ,i старших разрядов слова, формиI руемого блоком памяти 3, и нупей в остапь ных разрядах. Во втором такте по управпяю шеь.у сигналу, поступающему на вход 10, осуществляется сравнение кода на выходе коммутатора 4 с кодом, находящимся в выходном регистре 5 н сформированным в (ь -1)-ом цикне. Еслы код. с выхода коммутатора 4 меньша кода, записанного в выходном регистре. 8,то блок сравнени кодов 6 выдает единичный сигнал на выход 14, что свидетельствует о том, что очередной ъ -й разряд результата численно равен„1". Если этот код больше кода, записанного в выходном регистре 5, то блок сравнения кодов g выдает единичный сигнал на выход 13, что свидетельствует о том, что очередной разряд результата численно равен 1 . Если же ати коды равны, единичный сигнац не появляется ни на одном из выходов 13,14, что свидетельсв вует о том, что очередной разряд результата численно равен нулю. B третьем такте по управляющему сигналу, поступающему на вход 1 1, осуществляется прием кода в выходной регистр 5 с выхода коммутатора

4. В четвертом такте по управляющему сигналу, поступающему на вход 12, осуществляется сдвиг информации s регистре сдвига 1. Яа этом оканчивается один цнкп вь1числений. В результате выполнения М.циклов на выходах устройства. формируется последовательный код значения функции в избыточной двоичной системе счисления с цыфвами 1,0, 1 598070

Составитель М. Грибков

Редактор М. Трофимова Техреа И, Бабурка Корректор(С. Гарасиняк.

Заказ 1237/40 Тираж 826 Подписное

ПНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035,. Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент,.г. Ужгород, ул. Проектная, 4

Таким образом, устройство позволяет вычислять функции в неавтономном режиме, М, благодаря поразрядному вводу и выводу информации, имеет малое число внешних связей, что делает его удобным для ннтег1 рального исполнения.

Формула изобретения

Устройство для вычисления функций, содержашее регистр сдвига, группа выходов

;: котор01.о соединена с группой входов входного регистра, соединенного своими выходами с блоком памяти, выходной регистр, to т л и ч а ю m е е с я тем, что, с йелью расширения функциональных возможностей, оно дополнительно содержит коммутатор, блок сравнения кодов и элемент И, первый вход которого является входом устройства, выход соединен с управпякхпим входом входного регистра, группа выходов ре- 20 гистра сдвига соединена с первой группой входов коммутатора, вторая группа входов которого соединена с группой выходов блока памяти, группа выходов коммутатора соеди» пена с первой группой входов блока сравнения колов и с группой входов выходного регистра, труппа выходов которого соединена со второй группой входов блока сравнения кодов, первый и второй выходы блока сравнения кодов являются соответствующими выходамн устройства, лри этом второй вход элемента Р, управпякхпие входы регистра сдвига, выходного регястра и блока сравнения кодов являются соответственно первым, вторым; третьим и четвертым управпяюшими входами устройства.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Q 453739, кл. G 11 С 17/00, 1972.

2. Авторское свидетельстов СССР

М 390524. кл. Я 06 F 7/38, 1970.