Параллельный двоичный сумматор

Иллюстрации

Показать всеРеферат

f éC. бил.-.; я :е .ы л:

Союз Советских

Социалистических

Республик

{» 598971

{61) Дополнительное к авт. свид-ну (22) Заявлено12.07.71 (21}1682266д8/2 с присоединенйем заявки № (23) Приоритет (43) Опубликовано 15.03.78. Бюллетень №1 (61) М. Кл

G 06 Р 7/Э88

Гввударатввнный квиктвт

Вввата Мкнквтров СССР пв,авлаи кзвбрвтвнкй н вткрыткй

{53) УДК 681.325.54 (088.8) (45) Дата опубликования описаниФ17.02.78 (?2) Авторы изобретения

В. Н. Пахунов и О. С. Белкин (71) Заявитель (54) ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ СУММАТОР

Изобретение относится к цифровой вычислительной технике, в частности к устройст вам для суммирования чисел, представленных в двоичном коде.

Известны параллельные двоичные сумматоры, содержащие цепи формирования подготовительных функций и цепи одновременного формирования переносов для всех разрядов суммируемых чисеп Ц. Они характеризуют" 7 ся бопьшим количеством логических уров- 10 ней в цепях формирования переносов, что приводит к увеличению времени сложения.

Наибопее бпнзким к изобретению техническим решением является параллельный двоичный сумматор, содержащий в каждом И разряде эпементы И-НЕ и И-ИЛИ-НЕ, входы первого эпеменга И-ИЛИ-НЕ соединены с шинами инверсных кодов разрядов сла гаемых, входы второго элемента И-ИЛИ-НЕ соединены с шинами прямых и инверсных кодов разрядов слагаемых, выход первого элемента

И-ИЛИ-НЕ соединен со входом первого эпемента И-НЕ, выход второго элемента В

ИЛИ-НЕ соединен со входом второго элемента И-HE и со входами третьего элемента И-ИЛИ-НЕ„другие входы которого соединены с выходами первых и вторых элементов И-ИЛИ-HE всех предьтдушйх разрядов,(2). Этот известный сумматор требует значительных затрат оборудования и имеет недостаточно высокое быстродействие, что обусловлено задержкой на каждом из четырех погических уровней, 1Лепью изобретения является создание устройства позволяющего складывать два кисла эа меньшее, по сравнению в нзвесч ным сумматором время, т.е. имеющее меньшее количество логических уровней и требующее дпя реапизап ии меньшего оборудования. В описываемом сумматоре это достигается тем, что в нем выход второго элемента И-HE соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ предыдущего разряда, третий вход третьего элемента И-НЕ соединен с выходом третьего эпемента И-ИЛИ-HE предыдущего разряда, выход третьего эпеменга И-ИЛИ-НЕ и выход третьего элемента

598071

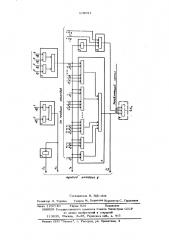

И-НЕ соединены, соответственно, с выходными шинвйи сумматора, На чертеже представлена схема одного разряда параллельного сумматора.

Он состоит из эпементов И-И ЛИ-H Е i 5 и 2, элемента И-HE 3, элемента И-ИЛИ-HF, 4, элементов И-НЕ 5 и 6, элемента 7 нагрузки, шнн 8 и 9 прямых и инверсных кодов разрядов слагаемых и выходных шин

10 сумматора.

Сложение двух чисел выпопняется по логической формуле.

Уп= Anа Впщ»"-» <, 0) где т» номер разряда сумматора: .

»5

Я» значение разряда суммы двух чисед

А Ят, спагаемые;

Сп» перенос нз младшего разряда.

Г1рн этом перенос С»» из 33 -го разряда за формируется одновременно лпя каждого разряда ио формуле (п п ) м» п: пу (д»»п+

+С©Т»Ти Т» Г K„»»„

Элемент И-ИЛИ-НЕ 1 вырабатывает сигнал, элемент И-ИЛИ-НЕ 2 вырабатывает сигнал Т1, элемент И-HE 3 инвертирует сигнап 3эпемент И-ИЛИ HE 4 вырабать»-! вает сигнал переноса б» элемент И-НЕ 5 инвер- тирует си гнан Г, элемент И-НЕ 6 выр абаты . ваетсигнап 8, ° СигнапыСо, К -Кх», Tj Т

» вырабагываются в мпадших разрядах сумма» тора. 40

В каждом разряде слагаемые А„и ИП подаются параллельно на входы элементов.

И-ИЛИ-НЕ 1 и 2, в результате чего на выходе вырабатываются сигналы Собствен» иый перенос Кп и Сумма по модулю два»

Ò . Элемент И-ИЛИ-НЕ 4 вырабатывает обратный код переноса С,. представляющий собой обратный код переноса иэ,разряд"без учета сигнала. "Собственный перенос К »1 т.е. по формуле (2) без первого чпена,";Элемент И-НЕ 3 инвертирует функцию сигнала Собственный перенос . Затем, как следует из формулы (1), дпя лопучения суммы 3 каждого разряда необходимо спожнть по Мо»»уп»о»»88 сигнал Тр и C»»-

linn этого в описываемом устройстве эпемент

И-НЕ 6 осуществпяет сборку снгнапов

Ò», К т1,» и», в результате чего с выходя эпемента И-HE 6 попучяют сигнал

I ж

8п и и-> = п+

Сигнап с выхода эпемента И-ИЛИ-НЕ 4 имеет вил

Cn = Ta aСи-».

Таким образом, сумма каждого разряда представляется усповно двумя сигналами, 1 олин из которых имеет значение». и в лру» гой 8> К схеме, испопьзукялей полученное значение суммы, необходимо подключать

o6a cHI Hana, составляющих сумму, FBK, чтобы реализовалась функция п= Сп

Формула изобретения

Параппепьный двоичный сумматор, содержащий в каждом разряде энементо" И-HE и И-ИЛИ-НЕ, входы первого элемента ИИЛИ-НЕ соединены с шинами инверсных кодов разрядов спагаемых, входы второго элемента И-ИЛИ-HE соединены с шинами прямых и инверсных кодов разрядов cnarac— мых выход первого элемента И-ИЛИ-НЕ соединен со входом первого элемента И-НЕ, вь»ход второго элемента И-ИЛИ-HE соединен с со входом второго элемента И-HE и со входами третьего элемента И-ИЛИ-НЕ, другие входы которого соединены с выходами первых и вторых элементов И-ИЛИ-НЕ всех предыдущих разрядов. о т и и ч а юш н и с я тем, что, с целью повышения быстродействия и сокраш ния оборудования, выход второго элемента И-HE соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-HE предыдущего разряда, третий вход третьего элемента И-HE соединен с выходом третьего элемента ИИЛИ-НЕ предыдущего разряда, выход третьего элемента И-ИЛИ-HE и выход третьего эпемента И-HE соединены»соответственно, с выходными шинами сумматора. 1

Источники информации, принятые во внимание при экспертизе:

1. Майоров С. A. и лр. Структура ШЗМ, Л., Машиностроение, 1970.

2. Мак-Сорпи, Выстродействуюп»ее .арифметическое устройство в двоичных вычислитепьных машинах. Труды института радиоинженер ов, % 1, 1 96 1 (русский перевод) .

508071

I е

3 ярИеМ этт бюшз g

Составнтепь В. Березкин

Редактор Л. Тюрина Техред М. Борисова Корректор С. Гарасиияк

Заказ 1 237/40 Тираж 826 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по депам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Фипиап ППП Патент, r. Ужгород, уп, Проектная, 4