Устройство для тестового контроля цифровых узлов

Иллюстрации

Показать всеРеферат

ОП MCAHHE

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Реслублик (11, 598082

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) За явлено 10.02.75 (21) 2103535/18-2 (51) М. Кл, Cj 06 F ll/04

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (43) Опубликовано 15.03.78. Бюллетень №10 (45) Дата опубликования описания07.03. > 8 (53) УДК 681.326.7 (088.8) (72) Авторы изобретения

B. H. Шуть> В. Н. Жубр и В. Л. Ноздренко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ТЕСТОВОЮ КОНТРОЛЯ

ЦИФРОВЫХ УЗЛОВ с присоединением заявки № (23) Приоритет

Изобретение относится к области электронной вычислительной техники и может быть использовано в аппаратуре контроля и настройки цифровых узлов ЭВМ.

Известно устройство для тестового контроля цифровых узлов, содержащее блок ввода данных, блок входных и эталонных выходных сигналов, коммутатор сигналов, блоки сравнения, индикации, управления, блок контролируемых выходов (1).

Основной недостаток этого устройства в .о сложность конструкции.

Наиболее близким техническим решением к данному изобретению является устройство для тестового контроля цифровых узлов, содержащее блок памяти, соединенный через блок записи информации с входами регистра теста, выходы которого соединены соответственно с первыми входами схем сравнения (2).

Это устройство обладает тем недостатком, что контакты проверяемого узла коммутируются вручную, вследствие чего на подготовительные операции уходит значительное количество времени, а участие человека в операции коммутации вносит. возможность погрешности при ее исполнении. Кроме того, необходимость иметь для каждого проверяемого узла таблицу коммутации при значительном количестве ти- 2 пов узлов создает неудобства при эксплуатации устройства.

Для повышения производительности и надежности контроля в предлагаемое устройство введены блок управления и блоки распознавания входов и выходов, причем первый, второй и третий выходы блока управления соединены соответственно с первым и вторым входами блоков распознавания входов и выходов и с управляющим входом блока записи информации, первые выходы блоков распознавания Bvoдов и выходов соединены с входами и выходами контролируемых узлов и со вторыми входами соответствующих схем сравнения, вторые выходы блоков распознавания входов и выходов соединены с третьими входами соответствующих схем сравнения, выходы которых соединены с входами блока управления, выходы регистра тестов соединены с третьими входами соответствующих блоков распознавания входов и выходов; кроме того, блок распознавания входов и выходов содержит делитель напряжения, узел дифференцирования, триггер, усилитель и реле, причем первый вход блока соединен с первым выводом делителя напряжения, второй вывод которого соединен с выходом блока и с первым контактом реле, третий вывод делителя напряжения соединен через узел дифферен598082

2$ цирования с первым входом триггера, второй вход которого соединен со вторым входом блока, а выход — со вторым выходом блока и через усилитель с реле, третий вход блока соединен ео вторым контактом реле.

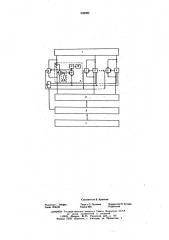

На чертеже приведена функциональная схема описываемого устройства для тестового контроля цифровых узлов 1, содержащего блоки распознавания 2 входов и выходов, схемы сравнения 3, блок управления 4, регистр теста 5, блок записи б и блок памяти 7. Каждый блок распознавания входов и выходов 2 содержит делитель напряжения 8, узел дифференцирования 9, триггер 10, усилитель 11, обмотку реле

l2, контакты реле !3.

Устройство работает следующим образом.

Контролируемый узел 1 имеет и контактов, каждый пз котовых может быть входным илн выходным. В блоке памяти 7 записаны тесты для его проверки. По младшкм адресам блока памяти 7 записан код соответствия входов и выходов, по остальным адресам — тестовые слова, которые представляют собой совокупность

«1» и «О», соответствующих входной комбинации и эталонной выходной реакции контролкруемого узла 1, Проверка осуществляется путем сравнения выходной реакции эталонного узла, записанной в блоке памяти 7, с реакцией контролируемого узла.

Перед проверкой узла 1 с блока управления

4 на нулевые входы триггера 10 каждого блока распознавания 2 подается импульс сброса, который устанавливает их в нулевое состояние.

Затем па первый вывод делителя напряжения

8 каждого блока распознавания 2 с блока управления 4 поступает импульс, соответствующий логической единице, Если первый контакт контролируемого узла 1 является входом, то на третьем выводе делителя напряжения 8 появляется единичный импульс, который через узел дифференцирования 9 поступает на единичный вход триггера 10 н устанавливает ro и единичное состгяние. С выхода триггера 10 потенциал логической единицы поступает через усилитель

11 на обмотку реле 12, ко-.орое, срабатывая, подключает вход контролируемого узла 1 к соответствующему ему выходу регистра теста 5, в который по сигналу нз блока управления

4 переписан из блока памяти 7 код соответствия входов и выходов. Схемы сравнения 3 сравнивают этот код с информацией, поступающей с единичных выходов триггеров 10. В случае, если информация совпадает, блок записи 6 считывает нз блока памяти 7 проверочное слово, заносит его в регистр теста 5, далее информация. поступает в схему сравнения, где сравнивается с выходной информацией контролируемого

-узла 1.

При несравнении хотя бы на одной иэ схем сравнения 3 из блока управления 4 на блок записи б поступает запрещающий сигнал. Несовпадение информации фиксируется индикатор@и, который иа чертеже не показан. При совпадении информации нз блока памяти 7 считывается следующее проверочное слово н т. д., пока узел 1 не будет проверен полностью.

Выходное напряжение узла дифференцирования блока распознавания входов и выходов

2 зависит от входного, то есть от перепадов потенциалов ка третьем выводе делителя напряжения "8, которые для выходных контактов контролируемого узла 1 вдвое меньше, нем для входных. Узел дифференцирования блока распознавания входов и выходов 2 настроен так, что когда ко второму выводу делителя напряжения 8 подключен выход контролируемого узла, на его выходе остается потенциал логического нуля. Тем самым контакты контролируемо о узла 1, являющиеся выходными, не коммутируются с выходами регистра теста 5.

Устройство для тестового контроля цифровых узлов позволяет производить коммутацию контактов проверяемого узла автоматически, за время значительно меньшее, чем в прототипе.

Конструктивное выполнение блока распознавания входов и выходов позволяет прн сравнении информации, полученной с единичных входов и выходов, обнаруживать неисправность входа или выхода, связанного непосредственно с контактом проверяемого узла.

Формула изобретения

l. Устройство для тестового контроля цифровых узлов, содержащее блок памяти, соединенный через блок записи ниформацик с входами регистра теста, выходы которого соедкнены соответ"твенно с первыми входами схем сравнения, отличающееся тем, что, с целью повышения производительности и надежности, в устройство введены блок управления и блоки распознавания входов и выходов, причем первый, второй и третий выходы блока управления соединены соответственно с первым и вторым входами. блоков распознавания входов и выходов и с управляющим входом блока записи информации, первые выходы блоков распознавания входов и выходов соединены с входами и выходами контролируемых узлов н со вторыми входами соответствующих схем сравнения, вторые выходы блоков распознавания входов и выходов соединены с третьими входами соот. ветствующих схем сравнения, выходы которых соединены с входами блока управления, выходы регистра тестов соединены с третьими входами соответствующих блоков распознавания входов и выходов.

2. Устройство по п. l, отличающееся тем, что блок распознавания входов и выходов содержит делитель напряжения, узел дифференцирования, триггер, усилитель и реле, причем первый вход блока соединен с первым выводом делителя напряжения, второй вывод которого соединен с выходом блока и с первым контактом реле, третий. вывод делителя напряжения соединен через узел дифференцирования с первым входом триггера, второй вход которого соединен со вторым входом блока, а выход — со вторым выходом блока н через усилитель с реле, третий вход блока соединен со вторым контактом реле.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 354415, кл. б 06 F 11/00, 19?О.

2. Авторское свидетельство СССР № 390526, кл. G 06 F 1!/04, 1971.

598082

Составитель 8. Крылова

Корректор Н. Тупица

Подписное

Texpe a О. Луговая

Тираж 626

Редактор С. Хейфиц

Заказ 1 236/40

11НИфПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

I l 3035, Москва, Ж-35, Раушская наб. д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4