Устройство для индикации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (>I) 898100 (61) Дополнительное к авт. свнд-ву (Я2) 3аявпено 06.01.76. (Я)23 11268/18-2 с присоединением заявки ¹(23) Приоритет (51) м. К,2

Cr 06 К 1S/18

Гваудврстввннай хвивит

eNNa Мннвтрав ССу

as доем ea6pemw9 в втхфипй (43) Опубликовано 15.03.78 Бюллетень %10 (53) VÄК 681.327..2 (088.8 ) (45) Дата опубликования описания 20.02.78 (72} Автор изобретения, е Йе Федоров (7l) Заявитель (>4) УСТРОАСТВО ДЛЯ ИНДИКАЦИИ

Кзобретение относится к области автоматики и Йачислительиой гехники.

Извес йиы устройства для индикации, содеритажие; индицируамые декады, коммутирующие элементы, блок опроса,, распределитель, 5 индикаторы, дешифраторы,,и. формирователи.

313.

Наиболее близким к изобретению по тех иической сущности -является:;устройство для индикации, содержашее цифровые индикаторы, !0 соединенные с коммутатором разрядов и ком-. мутатором cer ìeíòîâ, подключенным через дешифратор к ; блоку памяти, связанному с распределителем импульсов (2), Недостатком известных устройств являет. б cg иерегорание цифровых индикаторов црн отказе распределителя.

Цель изобретения - повышение надежности устройства.

Эта цель достигается тем, что предлага- Ю емок устройство содержит первые элементы

НЕ, соединенные с распределителем импульсов и первыми входами коммутатора разрядов, элементы ИЛИ, подключенные к распределителю, вторые элементы НЕ, связан- Ф ные с элементами ИЛИ, элементы задержки, соединенные со вторыми элементами НЕ, и третьи элемейтж НЕ, подключенйые ко вторым элементам HE и ко вторым, входам коммутатора разрядов.

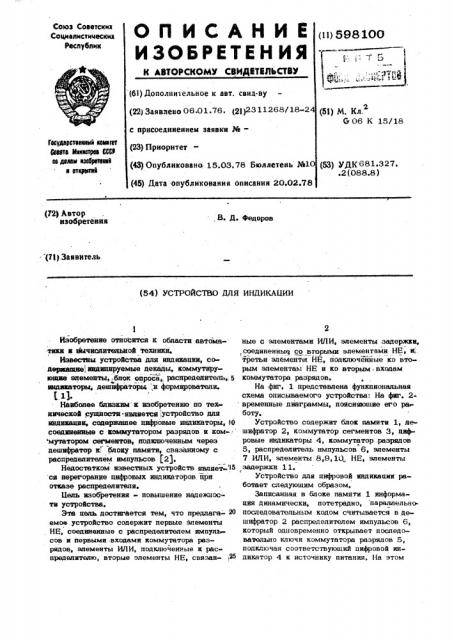

На фнг. 1 представлена функциональная схема описываемого устройства: На фиг. 2временные диаграммы, поясняющие егo ра боту, Устройство содержит блок памяти 1, дешифратор 2, коммутатор сегментов 3, цифровые индикаторы 4, коммутатор разрядов

5, распределитель импульсов 6, элементы

7 ИЛИ, элементы 8,9,10„. НЕ, элементы задержки 11.

Устройство для цифровой индикации работает следующим образом.

Записанная в блоке памяти 1 информация динамически, потетрадно, параллельно. последовательным кодом считывается в дешифратор 2 распределителем импульсов 6, который одновременно открывает последовательно ключи коммутатора разрядов 5, подключая соответствующий цифровой индикатор 4 к источнику питания, На этом

598 1ОО цифровом индикаторе 4 высвечивается цифра, соответствуюшая коду, поступаюшему на входы дешифратора 2.

Время засветки сегментов каждого цифрового индикатора 4 равно времени включения соотве тствуюшего ключа коммутатора разрядов 5.

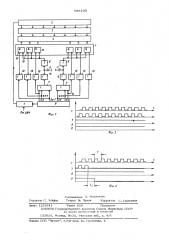

На фиг. 2 показана работа устройства зашиты цифровых индикаторов 4 при исправной работе распределителя импульсов 6. В 1о этом случае с выходов элементов 7 снимаются импульсы со скважностью =2 и сдвинутые на полпериода относительно друг друга. Элементы задержки 11, под» кпюченные параллельйо входам элементов 15

8, не успевают заряжаться до порога сраба тывания Ьтих элементов 8, тах как их постоянные времейи заряда вйбираются равными;

t, =RC1 =Р.С2 Ю где R — сопротивление зарядной пепи элементов задержки 11: Р - период следования импульсов на входах элементов 7.

Низкие потенциалы на элементах задерж- 25 ки ll иивертируются с выходов элементов

9 на четные и нечетные входы коммутатора разрядов 5, с которых подаются высокие потенциалы, разрешаюшие динамическую засветку цифровых индикаторов 4.

На фиг. 3, показан пример, когда распределитель импульсов 6 неиснравей и на одном er î выходе вместо импульсов формируется низкий потенциал длительностью, больше 35

В этом случае элемент задержки 11 за рядится за время до порога срабатывания элемента 8, с выхода которого подается запрешаюший сигнал на вход коммутатора разрядов 5, тем самым запрешая засвет4 ку цифровых индикаторов 4. Таким образом ключ коммутатора разрядов 5, принадлежаший неисправному выходу распределителя импульсов 6, будет закрыт, а цифровой индикатор 4 предохранен от статического тока.

Формула из обретения

Устройство для индикации, содержашее цифровые индикаторы, соединенные с коммутатором разрядов и коммутатором сегментов, подключенным через дешифратор к блоку памяти, связанному с распределичалем импульсов, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит первые элементы НЕ, соединенные с распределителем импульсов и первыми входами коммутатора разрядов, элементы ИЛИ, подключенные к распределителю импульсов, вторые элементы НЕ, связанные с элементами ИЛИ, элементы задержки, соединенные со вторыми элементами НЕ, и третьи элементы НЕ, подключенные ко вторым элементам НЕ и ко вторым входам коммутатора разрядов.

Источники информации, принятые so внимание при экспертизе;

1, Приборы и техника эксперимента 1, 1972Р с. 112

2. Лернер М.И. и др. Изд. "Энергия, 1970, с. 51.

Рит. 2

Составитель ° Ма РтвЯ "ов

Редактор С. Хейфиц Техред З. Чужик Корректор (. (âðàñèíÿê

3аказ 1238/41 Тираж 826 Подписное

ЦПИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открып и

113035, Москва, Ж-35, Рау цская наб., д. 4/5

Филиал ППП Патент", r.Óæãîðoä, ул. Проектная, 4