Устройство для индикации

Иллюстрации

Показать всеРеферат

Соктз Советских

Социалистических

Республик

onисАнИЕ

ИЗОБРЕТЕН И

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 21.07,76 (21)2387382/18-2 с присоединением заявки № (11 598102 (06 К 15/18

Государственный комитет

Совета Министров СССР по делам изаоретений и открытий (23) Приоритет (43) Опубликовано 15.03.78. Бюллетень №1 (45) Дата опубликования описания,03.03,78 (53) УДК 681.327 (088.8) (72) Авторы изобретения

H. Г, Глущук и Н. С. Малаший (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИНДИКА11ИИ месте любого десятичного разряда говорит о том, что перед этим десятичным разрядом должна быть запятая. Однако при этом способе индикации уменьшается полезная информационная емкость динамической памяти за счет искусственного увеличения разрядности хранимых чисел (вместо четырех двоичных разрядов используется пять двоиеных разрядов) °

1., Белью изобретения является увеличение полезной информационной емкости динамичеокой иамяти, т.е. увеличение надежности. В предлагаемом устройстве это достигается тем, что в 88Fo введены последовательно соединенные преобразователь кода циклов, блок сравнения и блок обнаружения запятой, выход которого соединен со входом блока ключей выбора запятой и блока отсчета циклов, выход которого соединен со входом преобразователя кода циклов.

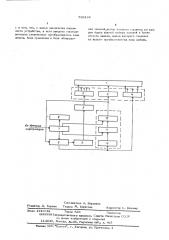

На чертеже показана блок-схема предлагаемого устройства.

Оно содержит блок 1 цифровых индикаторов, блок 2 ключей выбора символа, блок 3 клкгИзобретение относится к автоматике и вычислительной технике и может примениться в устройствах цифровой и знаковой индикации.

Известны устройства для индикации, содержатцие блок цифровых йндикаторов, соединенный с выходами блоков ключей выбора разрядов, цифровых символов и запятой, блок управления, соединенный со входом блока l0 динаЯИЧебйсф памяти и блока отсчета циклов, выход которого соединен с блоком ключей выбора разрядов и блоком буферной намяти, выход которого соединен с шифратором цифровых символов. Информация, находя- 15 тцаяся в блоке памяти, выводится на.цифровые индикаторы, причем на индикацию выводятся как целые, так и десятичные дробные числа.-,т1ля этого и блоке памяти для каждого цифрового символа (десятнчного раз- о ряде) отводится пять двоичных мест, из которых четыре двввичных места отводятся для хранения кода цифрового символа и одно двоичное место для указания запятой . Наличие логической 1" в пятом двоичном т

2 (51) М. Кл.

598102 чей выбора запятой, блок 4. ключей выбора разрядов, шифратор 5 символов, блок 6 динамической памяти, блок 7 управления, блок

8 отсчета циклов, блок 9 буферной памяти, преобразователь 10 кода циклов„блок 11 5 сравнения и блок 12 обнаружения запятой.

Во всех лампах блока 1 цифровых индикаторов все однотипные сегменты соединены параллельно и.представляют группы цифровых сегментов и запятой. Данные группы управ- 1О ляются блоком 2 ключей выбора цифровых символов и блоком 3 ключей выбора запятой, Блок ключей выбора разрядов коммутируют непосредственно или сетки ламп (в лампах типа ИВ), или анодное напряжение (в лампах типа ИН), Блок ключей выбора цифрс вых сйМволов управляется выходами шифратора 5 символов. Блок ключей выбора разрядов символов управляется от счетчика циклов. (цикл это время, в течение которого информация поступает со входа блока динамической памяти на ее выход). Количество разрядных ключей в блоке,4 равно количеству ламп индикации.

Информация от датчика информации (напри- мер, клавиатуры) в двоично-десятичном коде через блок 7 записывается в блок 6 динамической памяти.

В качестве блока динамической памяти можно BcHGUbsoBGTb) например, магнитострикЗО ционную линию задержки.

Блок 7 управления состоит иэ задающего генератора, счетчика текущего адреса, входного и выходного регистров.

Счетчик циклов блока 8 отсчета циклов. срабатывает по сигналу Конец цикла формируемого счетчиком текущего адреса блока

7. Одновременно сигнал "Конец цикла через блок 8 отсчета циклов осуществляет сброс блока 9 буферной памяти.

Сигнал "Конец цикла" выдается каждый раз после окончания цикла регенерации информации в блоке 6 динамической памяти, Код индицируемого символа в блоке 9 хранится в течение одного цикла.

Выходы дешифратора счетчика циклов блока 8 соединены с блоком 4 и входом преобразователя 10. кода циклов.

Преобразователь 10 преобразует поэи50 ционный код разрядов, поступающий на его вход, в двоична-десятичный или двоичный код (определяется кодом счетчика текущего адреса) цикла с опережением на единицу, Например, при индикации в и -ь цикле

-го символа на выходе преобразователя 10 будет соответствующий (двоична или двоично-десятичный) код цикла (1М + 1).

Этот код поступает Eki входы 6JIUKB 11 сравнения, на другие входы которого поступает код счетчика текущего адреса блока 7 управления. При сравнении кодов, на выходе блока 11 появляется сигнал, который управляет входом блока 12 обнаружении запятой. На другой вход блока 12 поступает информация с блока 7 управления. Блок 12 анализирует каждый символ информации, поступающей с блока 7, следующий эа индицируемым в данный момент времени символом. При обнаружении блоком 12 кода символа запятой он фиксируется .триггером, выход которого управляет блоком 3.

Таким образом, запятая индицируется одновременно с индицируемым символом в одной лампе и ц -м цикле (при использовании ламп индикации, имеющих сегмент запятой, например ИВ-6), Сброс триггера, фиксирующего запятую, производится сигналом, поступающим с блока 7. Он формируется счетчиком текущего адреса с опережением во времени на одно энакоместо по отношению к.сигналу Конец цикла . При сбросе триггера блока 12 на его выходе появляется сигнал, который поступает на вход счетчика циклов блока

8 отсчета циклов и изменяет его состояние на единицу. Счетчик переходит в состояние (rt+ 1). Следующий за ним сигнал счетчика текущего адреса блока 7 Конец

/ цикла изменяет также состояние счетчика циклов на единицу. Счетчик переходит в состояние (И + 2).

Таким образом, осуществляется автоматический пропуск знакоместа запятой.

Далее в блок 9 буферной памяти заносится следующий за запятой символ, который индицируется в следующей лампе.

Предлагаемое устройство позволяет более экономично использовать блок динамической памяти за счет определения запятой с опережением на один цикл, индикации ее в данном цикле и автоматическом пропуске одного цикла (при индикации числа с запятой.) ..

Ф ормул а изобрете ния

Устройство для индикации, содержащее. блок цифровых индикаторов, соединенный с выходами блоков ключей выбора разрядов, цифровых символов и запятой, блок управления соедине«цый со входом блока динамической памяти и блока отсчета циклов, выход которого соединен с блоком ключей выбора разрядов и блоком буферной памяти, выход которого соединен с шифратором цифровых символов, о т л и ч а ю щ е е5с В1 2

Ал

umph

Составитель A. Воронина

Редактор Л. Тюрина Техред М. Борисова Корректор С. Шекмар

Заказ 1240/42 Тираж 826 Подписное

Ш1ИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

113035, Москва, 2К-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 с я тем, что, с целью увеличения надежности устройства, в него введены последовательно соединенные преобразователь кода цикл ов, бл ок ср а вне ни я и бл ок об нар ужения запятой выход которого соединен со входом блока ключей выборе занятой и блока отсчета циклов, выход которого соединен со входом преобразователя коде циклов.