Запоминающее устройство

Иллюстрации

Показать всеРеферат

т

I,-, ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Соввтсних

Социалистических

Республик (" 598ыт

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 01.04.75 (21)2119482/24 с присоединением заявки _#_g 2128501 24 (23) Приоритет (43) Опубликовано 15.03.78.Бюллетень №1 (45) Дата опубликования описания 08,03.78

2 (51) М, Кл, 11 С 11 О0

Гасудврстаанный яамктат

Саватв Мнннстрав СССР аа далвм нзабратанна н аткрытнй (53) УДК 681,327. .6 (0S8.8) (79) Авторы изобретения А. А. Маслов, В, Я. Литуев, С. Ф. Мазанов и C. С, Александров

Всесоюзный научно-исследовательский институт нефтепромысповой геофизики (71) Заявитель

\ (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств. и может быть использовано в блоках памяти, содержащих дефек1 ные ячейки.

Известны запоминающие устройства, со- 5 держащие блоки памяти с дефектными ячей ками, . В них используются два идентичных интегральных блока памятй" и блок обжда

;: фектных разрядов (1 . НеаЮртаткям; этого, =тройства являются Венькин еппараалщ вте . Ю затраты, заключающиеся в удимийв ячеек: памяти.

Наибцпее близким цо технической сущнвс ти к изобретению является запоминающее устройство, содержащее блок памяти с де- Ы фектными ячейками, подключенный к блоку распределения информации по исправным разрядам, и регистр адреса (2).

Однако это устройство содержит допопюлелыый интегральыай блок оперативной

; амяти н эффективно может быть использовано при наличии большого числа дефектыъж ячеек, а также прн необходимости самовосстановления в процессе нормального функционирования. 25 й.сли кспичестао дефектных ячеек в интегральном блоке оперативной памяти отно» сительно невелико и нет необходимости в самовосстановлении, использование донов» нительного интегрального блока оперативной памяти для записи информации о дефектных ячейках (об отказах) является не оправданно избыточным по. количеству обо рудования и, кроме того, снижает наделе» ность устройства. .1йщью йастоящего изобретения является повышение надежности устройства.

Это достигается тем, что предлагаемое устройство содержит элементы И по числу дефектных ячеек и элементы ИЛИ по числу дефектных разрядов, входы элементов И цод» ключены к выходам регистра адреса, а выходы - к входам зпементов ИЛИ в coarse вин с законом распределения дефектных ячеек в. блоке памяти, входы блока распределения информации по, исправным разрядам соедв» нены с выходами элементов ИЛИ.

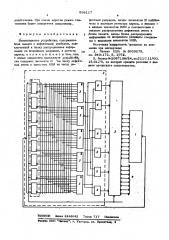

На чертеже приведена блок-схема предло женного запоминающего устройства.

598117

Устройство содержит блок памяти 1 с двфвхтными ячейками, подключенный к бло

«у 2 распрвделвния информации по исправ иым разрядам, соединенному с адресно-расщйритвльным блоком 3. Блок. 3, а сваю очередь, содержит tt .-разрядный регистр адреса 4, выполненный на триггерах, элементы И 5 по числу дефектных meea и влемен ты ИЛИ 6 но числу дефектных разрядов.

Входы элементов И 5 подклаочвны к выи щй дам регистра адреса 4, а выходы - к вхо дам элементов ИЛИ 6 в соответствии с законом распределения дефектных ячеек в блоке памяти, входы блока 2 соединены с выходами элементов ИЛИ 6. Блок 2 имеет 1й шины 7 приема-выдачи информации.

Работа устройства описана на примере интегрального блока памяти объемом 256

12-ти разрядных чисел.

Пусть блок памяги имеет дефехтные ячей-® ки по адресам:

b4 002 (код адреса QO000010) в 3, 8, 12 разрядах

М 017 (код адреса 00010001) в 1 и 10 раэрядащ ЗЬ

М 029 (код адреса 00011101) в 3 и 6 разрядшц

Ж 098 (код адреса 01100010) à 6 и 10 рвзр ядащ

М 229 (код адреса 11100101) в 1 и 12 30 разряд4щ

Для исключения влияния на работу уст ройства этих дефектных ячеек необходимо в адресно расширительном блоке 3 установить пять нтементов И 5 с количеством входов, З равным числу разрядов регистра адреса 4, и подключить к тем выходам регистра адреса 4, которые, соответствуют набору адреса с дефектными ячейками.

Например, при выбщзе ячейки bb 002 код ®О адреса соответствует 00000010 - состояшпо регистра адреса 4. Для получения единицы на выходе соответствующего шемента

И 5, необходимо входы последнего подсоединить к нулевым выходам регистра адреса

4 во всех разрядах, кроме второго, который следует соединить с единичным выходом второго разряда регистра адреса. Подобным образом да жны быть установлены остальные четыре элемента И 5 (в соответствии > с адресами 017, 02Э, 098, 229). Далее выходы элементов И 5 даажны быть подключены через элементы ИЛИ 6 к входам тех разрядов в блоке 2, которые соответствуют дефектным разрядам интегрального блока памятц 1. В нашем примере «опичество жюмвнгав ИЛИ 6 равно шести с максимальным числом входов, нв баиее двух, Осталь

93@в раэрщты блока 2 остаются незадейство .

4 ванными и в процессе функционирования будут всегда устанавливаться в такое состояние, которое отождествлено с Работоспособными разрядами.

В режиме записи информации. устройство работает следующим Образом.

Функционирование устройства начинается с момента прихода кода адреса, управляющих.. сигналов и информационного кода на шины 7 приема-выдачи информации. Согласно установившемуся коду адреса ячейка интегрального блока памяти 1 обнуляется .. В случае, если в ней имеются дефектные разряды, на выходе одного нз элементов И 5 возникает потенциальный сигнал, который через элементы ИЛИ 6 устанавливает в "единичное состояние только те разряды блока 2, которые соответствуют дефектным разрядам выбранной ячейки интегрального блока памяти 1.

Затем информационный код рассредотачйваеи, ся в блоке 2 и записывается в исправные разряды выбранной ячейки интегрального блока памяти 1. Во всех других случаях блок 2 в режиме, записи будет всегда уста» новпен в состояние, отвечающее работоспо собным разрядам, и информационный код будет записываться в интегральный блок памяти 1 в исправные разряды чисел без рассредоточения. При смене адресов режим записи будет аналогичным описанному.

Здесь следует отметить, что в оперативных запоминающих устройствах описанный про» цесс записи информации будет осушествпягься в режиме нормального функционировали иия а в постоянных запоминаюших устройствах только раз перед началом работы.

В режиме считывания информации устройст

so работает следующим образом.

При наличии кода адреса я управляющих импульсов информационный код считывает ся из интегрального блока памяти 1 в .блох

2. Параллельно адресный код подается в рв» гистр адреса 4 адресно-расширительного блока 3 и при наличии дефектов в разрядах выбранной ячейки интегрального блока нами ти 1, на выходе соответствуюшего элемента

И 5 появится потенциальный сигнал, который через элементы ИЛИ 6 - устанавливает в

1 единичное состояние только тв разряды бло ка 2, которые соответствуют дефектным paaps дам выбранной ячейки интегрального блока памзгги 1, Затем- информационный «од сосредотачизае гся в;блоке 2 и выдается на ши ны g приема-выдачи информации.

Вовсехдругихслучаяхблок2 врежиме считывания будет всегда установленв состояние, отвечающее работоспособным разрядам, и информационный код будет выдаваться иа шаны 7 приема-выдачи информации без соо5981 17

МНИИПИ Заказ 1246/42 Тираж 717 Подписное

Филйал ППП Патент, г. Ужгород, ул. Проектная, 4 редоточения. Прн смене адресов режим считывания будет аналогичен описанному., Формула изобретения у т

Запоминающее устройство, содержащее блок памяти с дефектными ячейками, подключенный к блоку распределения инфор .мании по исправным разрядам, и регистр адреса, о т л и ч а ю щ е е с и тем, что, t целью повышения надежности устройствЬ оно содержит элементы И по числу дефжтных ячеек и элементы ИЛИ по числу де- с б фектных разрядов, входы элементов Й поййФпе. чены к выходам регистра адреса, а выходы к входам элементos ИЛИ в соответствив с законом распределения дефектных ячеек в ,блоке памяти, входы блока распределения информации по исправным разрядам соедине ны с выходами элементов ИЛИ, Источники информации принятые во внимание при экспертизе:

1. Патент США 14 3658275, an. 340-172. 5. 1973.

2. Заявка %2097138/24,кл.611 С 11/ОО, 15.01r75, по которой npaaarp решениа о выдаче авторского свидетельства.