Квазистатическая ячейка памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социал истииеских

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (t>3 698119

t

2 (Я) M. Кл. (61) Дополнительное к авт. свид-ву (22) Заявлено 15,12,75 (21)2300269/18-2 с присоединением заявки № (23) Приоритет «« (43) Опубликовано 16.03.78.Бюллетень М 1 (45) Дата опубликования описания 08.03.78. (, 11 С 11 40

Гасударственный наннтат

Фавата Мнннстраа СОЛАР сс далаи нзабратвннй н атнритнй (53) УДК 681.327..66(088.8) (72) Авторы Ю. М. Герасимов, А. В, Калинин> А. Н, Кармазинский, изобретения В. П. Старенький и В. H. Чесноков

Московский ордена Трудового; Красного Знамени инженерно-физический институт (71) Заявитель

4 (54) КВАЗИСТАТИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области вычислительной техники и знектроники и может быть использовано при построении микромощных интегральных запоминающих устройств на дополняюших МДП-транзисторах.

Известна статическая ячейка, памяти, содержащая шесть МДП-транзисторов дополняю- . щих типов проводимости $1). Основным недостатком этой ячейки памяти является наличие ограничений на отношение размеров 10 транзисторов в режиме записи, в результате чего возрастает как активная плошадь, так и плошадьт: занимаемая ячейкой памяти на кристалле.

Этот недостаток 3л:®айен в квазиста- 15 тической ячейке. памяти, содержащей восемь

МДП-транзисторов допонияюшнх типов прово« димости (2). В этой ячейке памяти отсутствуют ограничении на отношение размеров транзисторов в режиме записи, и активная плошадь ячейки уменьшена приблизительно вдвое, однако плошадь ячейки на кристалле . практически не уменьшена.

Наиболее близкой по технической сушнооти к изобретению является кваэнстатичео- р5

2 кая ячейка памяти, содержащая триггер, выполненный на двух переключающих и двух нагрузочных. МИЛ-транзисторах дополняющих типов проводимости, управлявшие МДП-трав»: зисторы, стоки которых подключены к выха дам триггера, истоки - к разрядным шинам, а затворы - a адресной шине, и коммутирукьшие МДП транзисторы одного типа проводимости с нагрузочными транзисторами, стоки которых подключены K истокам нагрузочных.транзнаторов, истоки - к шине нулевого потенциала, а затворы - к адресной шине $2).

Недостатком известной ячейки памяти является сравнительно большое, число транзисторов и токоведуших шин в ней, в резуль тате чего усложняется структура топологического чертежа ячейки н увеличивается пло шадь, занимаемая ею на кристалле.

Для повышении надежности в предлагаемой ячейке памяти содержатся коммутирующие диоды, аноды которых подключены к истокам нагрузочных .МДП-транзисторов. а катоды - к разрядным шинам.

598119

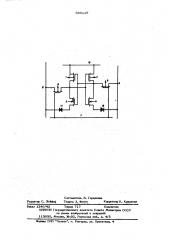

Схема описываемой ячейки памяти предЪ стаилеиа. на чертеже, где 1, 2 - переключающие транзисторы, 3. 4 - нагрузочные транзисторы, 5, 6 - управляющие транзистс рщ 7 » «адресная шина, 8, 9 - разрядные вины,10 - шина питания, 11, 12 -. комму-: тируюшие диоды

Ячейка памяти молит работать в режимах коавения, считывания и записи информации..

10 режиме храненнн потенциалы аа Ра фадиых шинах 8, 9 соответствуют логическо му. О, иа адресной шике 7 -логйческой 1 .

Управляющие транзисторы 5 н 6 закрыты, и ячейка сколь угодно донго хранят занисанную в яве информацию.

Прн считывании в исходном состОании потенциалы на разрядных шинах 8, 9 cocci аетствуют режиму хранения логическому З1 О", на адресную шину 7 подается сигнал, отпирающий управляющие транзисторы 5 и

6 - логический О ° Через ogaa нз управляющих транзисторов, подключенный к выходу триггера с уровнем логической 1 ., - 2S протекает ток, заряжающий соответствующую разрщ ную шину до уровня логической

"1 и тем самым указывающий состояние, ячейки.

В режиме записи информации на одну нз разрядных шин (например, 8), опреде-, ляемую кодом записываемой информации, . подается потенциал, соответствующий уровню логической 1, потенциал другой paspagиой шины (9) соответствует логическому

«О4, на адресно шину 7 подается уровень алогического "О.,отпирающий управляющие транзисторы 5 и 6. Один из коммутярум ших диодов (11), подкпюченный к разрядной шине с уровнем логической 1 закры- 4 вается и разрывает яетоковую цепь corn ветствующего нагрузочного транзистора (3).

В результате чего яа отношение размеров управлшащего (5) н нагруэочного (3) транзисторов ню накладываетса ограничение и размеры всех транзисторов в ячейке можно выбирать" одинаковыми я минямальньм ми. Запись ннфорМацни в предложенной ачеиие происходит так же, как н в динамических ячейках - путем заряда узловой емкости на выходе триггера через управляющий транзистор.

Однако коммутирующие диоды 11 я 12 предназначены не для Осуществления динамической записи информация в ячейку, а

Ю

55 для предотвращения сбоев в невыбранных ячейках пря изменении потенцяапов на раз ряднах шинах. Поскопьку в этих ячейках в одном из плеч триера могут быть закрыть/

66 переключающяй тряпэястор» яагруэОчный транзистор и коммутирующий диод, то узпс вая емкость на выходе этого плеча трит» гера может заряжаться с постоянной време ни, определяемой токами утечки закрытых транзисторов. Поэтому в режиме записи и считывания в запоминающем устройстве, достроенном на основе данной ячейки, накладывается ограничение на длительность управляюпшХ импульсов сверху (не более единнцмс), Следует заметить, что коммутирующие диоды 11 и 12 могут быть включены пь только в истоковую, но и в стоковую цепь нагрузочных транзисторов. Выбор того ила иного способа включения диодов можно осуществить, исхода as наиболее простой структуры топологического чертежа при заданной технологии. Вместо диодов можно испольэовать и МДП-транзисторы в диодном включении.

Предлагаемая квазнстатическая ячейка памяти содержит на два транзистора и на одну токоведущую шину меньше, чем известная, что позволяет значительно уменьшить площадь, занимаемую ею на кристалле.

Наиболее полно достоинства ячейки реализуются при ее изготовлении по тежологйи кремний на сапфире, где для изготовлеййя диодов по существу не требуется дополннтель ный пл Ошади»

Прорисовка топологических чертежей раз личных ячеек для этой технологии показала, что площадь, занимаемая предлагаемой квазнстатнческой ячейкой на кристалле, на

25-30 Ъ меньше, чем у известных стат»ческих н квазястатических ячеек.

Формула изобретения

Квазнстатическая ячейка памяти, содержащая триггер, :" выполненный на двух переключающих я двух нагрузочных МДП-транзисторах дополняющих типов проводимости я управляющяе Mlle-транзисторы, стоки которых подключены к выходам триггера, истоки - к разрядным шинам, а эатворык адресной. шине, отл и чаюша ас а тем, что, с целью повышеняа надежности ячейки, она содержят,коммутирующие диоды, аноды которых подключены к истокам нагрузочных МЛП-транзисторов, а катоды— к разрядным шянам.

Источники янформвцяя, принятые во вяи» мание пря экспертизе:

1. Патент США, l4 3521242, кл. 340-173, 1 972.

2. Заявка bb 2039470/24, кл. Q 11 С 11/4C:, 26,06.74, по которой принято решеняе о выдаче авторского свидетельства.

598119

Составитель.В. Горданова

Редактор С. Хейфец Текред 3, Фанта, Корректор Н. Кованева

Заказ 1246/42 Тираж 717 . Подписное

0НИИПИ Государственного комитета Совета;Министров СССР но делам изобретений н открытий

113035, Москва, Ж35, Payracaas наб., д, 4/5

Филиал ППП Патент, г. Ужгород, уп. Проектная, 4