Устройство для синхронизации контрольного и эталонного цифровых сигналов

Иллюстрации

Показать всеРеферат

!

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (и) 598226 (61) дополнительное к авт. свид-ву— (22) Заявлено 240576 (23) 2364765/18-21 с присоединением заявки Ph— (23) Приоритет (43) Опубликовано 150378. Бюллетень Рй 10

2 (51) М. Кл.

H 03 К 5/153

Гоеиаретаанный ноантат болата MNNNNTGNI GGGP но ланов наойрнтнннй н отнрытнй (5З} УДК 621. 316. 729 (088. 8) (45) Дата опубликования описания гО.О2.78 (72) P âòîpû изобретения

A.B.Êóðèëoâ и В.A.Òàðàñoâ (7а) Заявитель (54) УСТРОИСТВО ДЛЯ СИНХРОНИЗАЦИИ КОНТРОЛЬНОГО

И ЭТАЛОННОГО ЦИФРОВ61Х СИГНАЛОВ

Изобретение относится к области полупроводниковой импульсной техники и может найти применение при построении аппаратуры тестирования и настройки оборудования цифровых систем 5 связи и вычислительной техники.

Наиболее близким техническим решением к данному изобретению является устройство цикловой синхронизации,содержащее регистр сдвига, дешифратор, 10 блок выделения тактовой частоты, генератор> элементы И элемент НЕТ и счетчикй импульсов (11 .

Однако при решении некоторых задач вычислительной и измерительной 16 техники, а также для тестирования и контроля работоспособности аппаратуры линейных трактов ИКМ-систем, известное устройство обладает рядом недостатков. Такое устройство сложно, поэтому его трудно реализовать для высоких тактовых скоростей.Оно содержит большое количество элементов, что требует существенных аппаратурных затрат.

С целью повышения быстродействия и надежности в устройство для синхронизации контрольного и эталонного цифровых сигналов, содержащее элемент

НЕТ, блок выделения. тактовой частоты, вход которого подключен к шине контрольного сигнала, первый выход блока выделения тактовой чатоты соединен со входом счетчика импульсов, выходы которого через дешифратор подключены к первым входам первого и второго элемента И, выход второго элемента И соединен с первым входом генератора эталонных сигналов, второй вход которого подключен к выходу блока выделения тактовой частоты, введены элемент

НЕ, Н6-триггер и блок несовпадений, выход которого соединен с первым входом элемента НЕТ, второй вход которого подключен к последнему разряду счетчика импульсов, а выход элемента НЕТ соединен с одним из входов RS-триггера, другой вход которого подключен к второму выходу дешифратора, причем выход RS-триггера соединен со вторым входом второго элемента И непосредственно и через элемент НЕ со вторым входом первого элемента И, выход которого подключен к третьему входу генератора эталонных сигналов, выход которого соединен с первым входом блока несовпадений, второй вход которого подключен к шине контрольного сигнала. 4

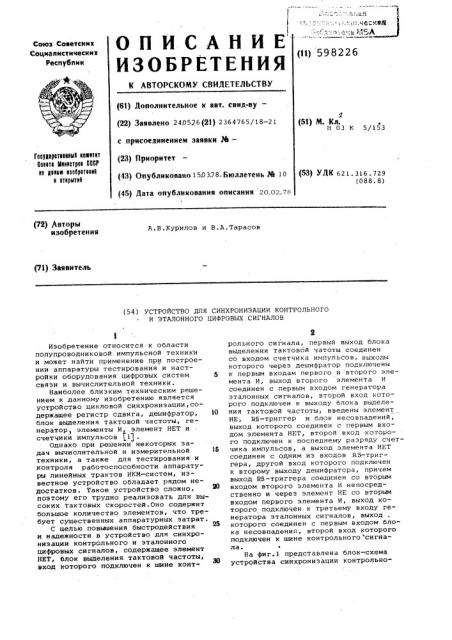

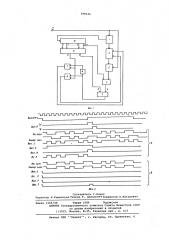

На фиг. 1 представлена блок-cxgMa устройства синхронизации контрольно598226 го и эталонного цифровых сигналов; на фиг.2 — временные диаграммы его работы (а — работа устройства при отсутствии синхронизации, б-момент вхождения в синхронизацию). 5

Устройство синхронизации контрольного и эталонного цифровых сигналов содержит блок выделения тактовой частоты 1, генератор эталонных сигналов

2, блок несовпадений 3, элемент HET 4, )0

R5, — триггер 5, элементы И 6, 7, элемент НВ 8, дешифратор 9, счетчик импульсов 10 v. шину контрольного сигнала 11.

Устройство работает следующим обра- )> зом.

Контрольный сигнал по шине 11 одновременно поступает на блок 1 и блок

3. Блок 1 запускает генератор 2 и счетчик 10. На блоке 3 производится поразрядное сравнение контрольного и эталонного слова длиной 2 разрядов (бит). Сигнал наличия первого несовпадения в выделенном слове устанавливает на выходе триггер 5 в единичный

И потенциал (фиг. 2, вых. 5) . В этом случае при поступлении сигнала с выхода а дешифратора 9 на элемент 6 формируется сигнал сдвига эталонной последовательности на такт.

Сигналу наличия несовпадений разрешается устанавливать на выходе триг-. гера 5-единичный потенциал в первые

2 тактов работы счетчика 10, что соответствует длине выделяемого слова, в течение последующих 2 тактов pat7 36 боты счетчика 10 — запрещается. Считывание состояния триггера 5 сигналом с выхода а дешифратора 9 и установка на выходе триггера 5 нулевого потенциала с выхода в дешиф- 40 ратора 9 производится после осуществления запрета перестановки триггера 5 сигналом несовпадений, причем установка на выходе триггера 5 нулевого потенциала должна осуществляться после 45 окончания считывания состояния триггера 5 ..

Цикл повторяется до того момента, . когда в течение 2 тактов не будет н зафиксировано несовпадений. В этом Q) случае, в момент наличия сигнала на выходе а дешифратора 9, на элементе 7 формируется сигнал окончания синхронизации. Следовательно, на выходе элемента )5 формируется сигнал продолжения синхронизации Сдвиг эталонной последовательности на такт (фиг.2, вых. 6), а на выходе элемента 7 формируется сигнал Окончание синхронизации (фиг.2, вых.7), отключающий Устройство. Введение дополнительного (п +1) -го разряда счетчи-, ка 10 позволяет исключить влияние внутренней задержки в цепи, состоящей из узлов 2-3-4-5-6(8-7)-2 и разделить во времени фиксацию несовпадений, их считывание и возвращение триггера 5 в исходное состояние.

Формула изобретения

О

Устройство для синхронизации контP ольного и эталонного цифровых сигналов, содержащее элемент НЕТ, блок выд еления тактовой частоты, вход которого подключен к шине контрольного сигнала, первый выход блока выделения тактовой частоты соединен со входом счетч ика импульсов, выходы которого через м дешифратор подключены к первым входа первого и второго элемента И, выход второго элемента И соединен с первым входом генератора эталонных сигналов, второй вход которого подключен к выходу блока выделения тактовой частоты, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности устройства, в него введены элемент НЕ, R5-триггер и блок несовпадений, выход которого соединен с перв м

ы входом элемента HETÄ второй вход аз яоторого подключен к последнему ра р— к т ду счетчика импульсов, а выход эл мента HET соединен с одним из входов

ВВ-триггера, другой вход которого подключен к второму выходу дешифратора, причем выход Нб-триггера .соединен со вторым входом второго элемента И непосредственно: И через элемент НЕ со вторым входом первого элемента И, выход которого подключен к третьему входу генератора эталонных сигналов, выход которого соединен с первым входом блока несовпадений, второй вход которого подключен к шине контрольного сигнала.

Источники информации, принятые во внимание при экспертизе:

1. Левин Л.С., Плоткин М.A. Основы построения цифровых систем передачи.

М., Связь, 1975р с. 117.

598226

ФЬг. /

Выл У а

Вых 9

"ь"

3н. сигн.

Ианпьр. сиги.

Эык. 8

Вых. В арык. д

Вх. 9

Ул. сигн.

Мантр. сигм.

Вых. а

Вмх. Х

Вил, 1

Составитель Г.Ильин

Редактор Н.Каменская Техред Е. Давидович Корректор II.Ìàêàðåâè÷

Заказ 1269/48 Тираж 1086 Подписное, ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4