Цифровой спектральный анализатор

Иллюстрации

Показать всеРеферат

.1

К АВТОРСКОМУ СВИДЕТГЛЬСТВУ (63) Лоиолннтельное и авт. свид=ву (22) Заявлено 180275 (21) 2106522/18-24 с присоединением заявки № (23) Приоритет (4З) Оиуоликоваио 250 ç78 Ьюллетеиь _#_=-11 (45) Дата оп бликований описании 250278 (51) М. Кл.

С 01 Й 23/00

& 06 С 7/52

l 06g3$6TR600Qll N06i6T0T

0030т6 бт6006Ц06 MN

60 Р06к 06И 6т60М

0 0тирити9 (53) УДЕ 681.8 (088. 8) (72) Автори изоДретеиив А.Ф.Борнгардт, A.È.ÈoãèëüHÈöêèé,. П,В.Новиков и О.Н.Лковлев

p3) Заявитель Ордена 1рудового красного знамени бюро аналитнческогo приборостроения (54) ЦИФРОВОЙ СПККтрАЛЬНЫЯ АНАЛИВАтОР

Изобретение относится к измерительной технике, в частности к многоканальным аналнзаторам спектра для получения текущих оценок спектральной плотности случайных процессов и выявления скрытых периодичностей, начало и длительность которых неизвестны.

В технике спектрального анализа известны многоканальные аналоговые спектроанализаторы, содержащие усили- 60 тели, избирательные фильтры, детекторы и фильтры нижних частот (1).

Эти анализаторы BbcTpoeHEz с использованием средств аналоговой техники, что вызывает значительные технические трудности при их реализации, особенно в области инфранизких частот.

К недостаткам таких спектроанализаторов относятся нестабильность параметров, низкая точность, необходимость Я применения. большого объема оборудова-. ния для анализаторов, работающих в широком диапазоне частот.

Известны также цифровые спектроанализаторы, основанные на применении 25 дискретного и быстрого преобразований

Фурье. Один из таких анализаторов $2) является наиболее близким по техничесГ кому решению g изобретению. Анализатор содержит бФзт(оперативной памяти, Зп первый вход которого соединен с выходом арифметического блока, а выход подключен к входу блока сглаживания, выход которого является выходом анализатора, а управляющий вход соединен с первым выходом блока управления, второй выход которогo подключен к управляющим входам арифметического блока и блока оперативной памяти, а третий выход — к управляющему входу блока определения текущей фазы, информационвый вход которого является первым входом анализатора.

Вычнслейие оценок спектральной плотности в таких анализаторах производится по отдельным участкам реализации анализируемого процесса, что затрудняет, а при малых отношениях сигнал — шум делает невозможным выявление скрытой периодичности или других нестационарностей процесса, которые имеют конечную длительность н могут начинаться в произвольный момент времени. Более того, анализатор не пригоден для получения текущих оценок спектральной плотности в широком частотном диапазоне в реальном масштабе врюлени, так как расширение частотного диалазона в этом случае требует значительных затрат оборудования для запоминания

599221 „М Ь >з. К, (Ра), а)

1 где bf — минимальный шаг частотного анализа, определяющий интервал между частотами настройки избирательных Фильтров)

k — номер гармонии (частотного канала) .

Счет величин г ведется по модулю

2 . Значение Ь является конструктивной постоянной, определяемой числом разрядов соответствукщего регистра в блоке 2 фазы. При k 1 и полном заполнении регистра фазы должно выполняться соотнскаеиие gf Тд 1, что соответствует периоду гармоничностей функции

9< Z5t. Следовательно, ь 1 =2-, к й" 2 (znad Z ) g

Ф)

Выходной величиной блока 2 является двоичный код числа h1k 2(2)h с размерностью л 2 радиан, учитывсей реализации исследуемого процесса, усксрения операции умножения и увеличения числа коэффициентов разложения.

Цель изобретения — расширение частотного диапазона анализатора, обеспечивающее текущую оценку спектральной плотности в широком частотном диапазоне.

Это достигается тем, что в анализатор введены блок постоянной памяти и блок задержки установки адреса, вход которого соединен с четвертым выходом блока управления, а выход подключен ко второму входу блока оперативной памяти, второй выход которого соединен е первым и со вторым âõîдами ариФметического блока и с выходом блока постоянной памяти, первый вход которого является вторым входом анализатора, второй вход соединен с выходом блока определения текущей фазы, а управляющий вход подключен ко второму выходу блока управления.

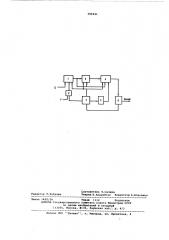

На чертеже представлена структурная схема предлагаемого цифрового анализатора, Анализатор содержит блок 1 постоянной памяти, блок 2 определения текущей Фазы; арифметический блок 3, блок

4 оперативной памяти, блок 5 задержки установки адреса, блок б сглаживания и блок 7 управления. Выход блока сглаживания является выходом анализатора.

На первый вход блока 1 постоянной памяти поступают отсчеты анализируемого процесса f в двоичном коде, а на вход блока 2 вычисления текущей фаэиномер этого отсчета г . Период поступления входной информации То равен периоду квантования процесса во времени. Текущая фаза гармонической функции 9 вычисляется по формуле ваемой в блоке 1 постоянной памяти.

Вычисленная, таким образом, фаза, а также величина f„ в двоичном коде образует адрес обращения к блоку 1 пос5 тоянной памяти. Блок 1 выполнен на основе долговременного запоминающего устройства и содержит всевозможные произведения (. +jan(zxbf Тр 1 к }

1С для Фазы в пределах от О до й/2,где — коэффициент, определяющий постоянную времени,осреднения и, соответственно, полосу пропускания. Он Bbi1 бирается конструктивно кратным целой б отрицательной степени двойки,т.е. 2 .

Величины произведений для фазы более

Й /2 отличаются только знаком, который определяется в блоке 7 управления на основе анализа соответствующих разЩ рядов регистра фазы. Арифметический блок 3 вычисляет текущие значения коэффициента разложения по алгоритму

+<,„=cL>,-L a„., L f si, Ы т,wg

I СОь2ЛЪ Т >k. (Ъ)

Произведение (f„dos(2RT< "k df ) определяется с помощью блока 1 путем

ЗО формирования в блоке 2 фазы, отличающейся от фазы синуса на /2 ° Выходной величиной блока 2 при этом является двоичный код

М к htk Ф2

Величины с и В„ „ выбираются из определенных Ячеек блока 4 оперативной памяти, адрес которых зависит от и подаются на второй вход, а также на младшие разряды первого входа арифметического блока, чем обеспечивается вычисление произведений (й„,. 1 И L Ь„,. путем сдвига впрайб на Ч разрядов.

46

Из выражения (2) следует зависимость между минимальными шагом частотного анализа и периодом квантования

of=

Тз (4)

„. Г тС;, ляемое в блоке б, моделирует выходное напряжение избирательного фильтра, частота настройки которого равна а полоса пропускания 6 «- - тО

Для упрощения аппаратурной реализации фильтров величина б1 выбирается равной

"То Тр (5)

В спектроанализаторах полоса пропуска6О 1 ия If и шаг частотного анализа ьф должны быть разны, поэтому иэ выражений (4) и (5) следует, что цФ2. (б) выражение (6) определяет связь между

6бконструктивными постоянными анализа599221 тора. Работой всех устройств анализатора при выполнении операции вычисления фазы, обращения к блокам 1 и 4, вычисления коэффициентов d.» „,Ь„ „,с»,. синхронизирует блок 7 управления °

Пусть на вход анализатора поступил очередной г -й отсчет анализируемого процесса р. Блок 2 вычисляет фазу начальной (первой) гармоники k» = к, т.е. Mk = k . По адресу, составленному из двоичных кодов, иэ блока 1 постоянной памяти выбирается произведение (. .„ь и (2Щ T() ", ) ()0 а из блока 4 оперативной памяти по адресу, например А, выбирается значение коэффициента a. „-, и арифметический блок 3 определяет -величину a»„i

/ которая запоминается в блоке 4 оперативной памяти по адресу А1. Для опре- З) деления величины 6„ „ из блока 1 постоянной памяти по адресу, составленному из двоичных кодов f„ N k, выбирается произведение (. .„ьбп (2ЩТог с + 2h1 Г г ), а из блока 4 оперативной памяти по другому адресу A „ — значение коэффициента 6» „, арифметический блок on- y ределяет величину 6», которая запоI минается- по адресу А °

Далее блок 2 вычисляет фазу синуса и косинуса второй гармоники gk = (k+<) иМ k =M» + ;Й+, .а из блока 1 выбира1 ,ются произведения по адресам, составленным из двоичных кодов „,ЯМ и

f„Z kZ . Иэ блока 4 оперативной памяти по адресам A< i и A +1 выбираются величины а» и 6» < и арифметичес1 кий блок 3 определяет величины а» и 6», кото ые запоминаются по адресам А, -1и А +1 . Пусть в процессе вычисленйя тп -ой и m+1-ой гармоник адрес ячейки блока 4 оперативной памяти сохранился постоянным и равным

h<+(m+1). При этом произойдет двойное обращение к одной и той же ячейке памяти за величинами а», -1 и (ц, что приведет к уменьшению постояйной времени осреднения и расширению поло- @ сы в 2 раза. Управление адресами обращения к блоку 4 оперативной памяти осуществляет блок 5 н зависимости от номера гармоники k . . Например,,коэффициенты разложения от k до k могут вычисляться и храниться н индивидуальных ячейках памяти от k „ до » „,:Н .одной ячейке дна коэффициента, от К2тдо ka — в одной ячейке три коэффициента. Это приводит к тому, 60 что полоса пропускания моделируемых избирательных фильтров будет равна соответственно 8, 2Pf i 3&j

Частотный диапазон анализа ьР определяется как ьР (» щ-k f)=6m ëj а число занятых оперативных ячеек па" мяти равно при этом Зщ. Величина спектральной плотности, вычисляется н блоке б, где происходит также сглаживание этой оценки. Период обращения к блоку 4 оперативной памяти при нычислении коэффициентов С „,. больше

Tz, так как а„ „ и 6„ „изменяются медленнее, чем входной процесс. После завершения вычисления коэффициентов а» и Ь» для r -го отсчета, через время Т берется новый t + 1 отсче процесса Ф и вычисляются козффиФ циенты о„„„и 6 формула изобретения

Цифровой спектральный анализатор, содержащий блок оперативной памяти, первый вход которого соединен с выходом арифметического блока, а выход подключен к входу блока сглаживания, выход которого является выходом анализатора, а управляющий вход соединен с первым выходом блока управления, второй выход которого подключен к управляющим входам арифметического блока и блока оперативной памяти, а третий выход — к управляющему входу блока определения текущей Фазы, информационный вход которого является первым входом анализатора, о т л и ч аю шийся тем, что, с целью расширения частотного диапазона анализатора, в него введены блок постоянной памяти и блок задержки установки адреса, вход которого соединен с четвертым выходом блока управления, а выход подключен ко второму входу блока оперативной памяти, второй выход которо" го соединен с первым и со вторым вхо" дами арифметического блока и с выходом блока постоянной памяти, первый вход которого является нторым входом анализатора, нторой вход соединен с выходом блока определения текущей фазы, а управляющий вход подключен ко второму выходу блока управления.

Источники информации, принятые но внимание при экспертизе:

1. Калинчук Б.A., Пиастро В.П.

Анализаторы инфразвуковых случайных процессов. Л., Энергия, 1973, 2. Прикладной анализ случайных процессов. Сборник научных трудов. (Сибирское отделение AH СССР) Новосибирск, 1973.

599221

Составитель Э.Сечина

Техред Н.Андрейчук Корректор А.Власенко

Редактор Т.Зубкова

Филиал ППП Патент ", г. Ужгород, ул. Проектная, 4

Заказ 1402/36 ТиРаж 1112 Подписное

1111ИИПй Государственного комитета Совета Министров СССР по делам изобретений и открытиЕ

113035, Москва, Ф-35, Рауюская наб., д. 4/5