Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

(11) 599265

Союз Советскин

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) ЗаЯвлено 08 07.75 (21) 2155608/18-24 с присоединением заявки № (51) М. Кл.

G- 06 Р 7/38

Госуде Рстеенный комитет

Совете Мнннстрое СССР оо делам нзобретеннй и отнрытнй (23) Приоритет (43) Опубликовано 25.03.78. Бюллетень №1 1 (45) Дата опубликования описания 02.03.78. (53) УДК 681.325 (088.8) (72) Авторы изобретения

А. Л. Рейхенберг и P. Я. Шевченко (71) Заявитель (54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Предпагаемое устройство относится к обпасти цифровой вычиспитепьной техники и может найти применение в специализированных арифметчческих устройствах и системах автоматического управпения. 5

Известны устройства дпя извпечения квадратного корня, содержашие, регистры, сумматоры, дискриминаторы и бпоки формирования констант (1)..

Недостаток этих устройств — относитепь- g. но низкое быстродействие и сложность реапизации.

Наибопее бпизким к предпоженному изобретению по технической сущности явпяется цифровой функциональный преобразоватепь, содержащий бпок управпения три накопительных регистра, первые входы которых соединены с первым, вторым.и третьим выходами блока управления соответственно регистр сдвига>вход которого соединен с четвертым 20 выходом блока управления, четыре сумматора - вычитатепя дискриминатор знака, выхо/ ды которого соединены с управляющими входами сумматоров-вычитатепей выходы первого, второго и третьего сумматоров-вычита- 25 тепей соединены с вторыми входами соотвегствуюших накопительных регистров; первые б выходы первого и третьего накопитепьных регистров соединены с первыми входами соответствующих сумматоров-вычитатепей, а вторые выходы этих накопитепьных регистров соединены с первым и вторым входами дискриминатора знака соответственно, второй выход второго накопительного регистра соединен с первым входом второго сумматора-вычитатепя бнок формирования констант, J вход которого соединен с пятым выходом бпока управпения, а выход — со вторым входом первого сумматора-вычитателя Pj

Недостаток такого устройства — низкое быстродействие и относитепьно бопьшой объем аппаратуры.

Цепь изобретения — повышение быстродействия и упрощение устройства.

Это достигается тем, что в предпоженном преобразоватепе выход регистра сдвига соединен со вторым входом второго и первым входом четвертого сумматоров-вычитатепей, первый выход второго накопительного регистра соединен со вторым вхо599265 дом четвертого сумматора-вычитате пя, вы-. ход которого соединен со вторым входом третьего сумматора-вычитателя.

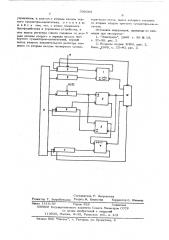

На чертеже изображена блок-схема цифрового функционального преобразователя.. 5

Цифровой функционапьный преобразоватепь состоит из одноразрядных сумматоров-вычитатепей 1-4 комбинационного типа, накопитепьных регистров 5-7, регистра 8 сдвига, блока 9 формирования констант, дискримина-щ тора 10 знака и блока 11 управления, Выходы сумматоров-вычитатепей 1,2, и 4 соединены с информационными входами накопительных регистров 5-7 соответственно, а выходы поснедних соединены с первыми 15 входами указанных сумматоров- вычитате пей.

Второй выход накопительного регистра 6 соединен со вторым входом сумматора-вычитателя 3, выход которого соединен со вторым входом сумматора-вычитателя 14. 20

Выход регистра 8 сдвига соединен с первыМ входом сумматора-вычитатепя 3 и вторым входом сумматора-вычитатепя 2. Выход блока

9 формирования констант соединен с входом сумматора-вычитатепя 1. Вторые (зна- 25 ковые) выходы накопительных регистров 5 и 7 соединены с входами дискриминатора

10 знака. Первый выход поспеднего соединен с управляющим входом сумматора-вычитатепя 1, второй выход - с управляющими 3О входами сумматоров-вычитатепей 2 и 3, третий выход — с управляющим входом сумматора-вычитатепя 4. Входы накопитепьных регистров 5-7, регистра 8 сдвига и блока

9 соединены с выходами бпока 11 управпе- 35 ния. Блок 9 формирования констант выполнен, например, в виде одностороннего запоминающего устройства ипи регистра сдвига.

441)

Он генерирует на выходе константы вида 2 где ф -номер итерации. Первый выход 40 накопительного регистра 6 выполнен от выхода предпоспеднего разряда регистра.

Дискриминатор 10 знака состоит из погических эпементов и триггера. Блок 11 управления состоит из генератора тактовых 45 импульсов, счетчика, распредепитепя и погических элементов. Входами устройства являются: вход, накопительного регистра 5 дпя аргумента с, вход регистра 8 сдвига дпя аргумента Х в первом цикле вычиспе- 50 ния и для аргумента 2 во втором цикпе вычисления. Выходом устройства явняется выход накопительного регистра 5.

Цифровой функциональный преобразоватепь работает спедующим образом.

Первоначально регистры 5-8 и блок 9 устанавливаются в нулевое состояние. В первом цикпе вычисления B накопительный регистр 5 в параппепьном двоичном коде подается значение аргумента,(, в регистр

8 сдвига — значение аргумента Х. Каждый цикл вычиспения состоит из 2 итераций, где Л-число разрядов аргумента. Ячейки, состоящие из накопительных регистров 5,6 и 7 и сумматоров-вычитатепей 1,2 и 3,4, в каждой итерации работают параплепьно.

Разностно-итерационный алгоритм; реапизуемый в предложенном устройстве, основан на представлении любого двоичного чиспа.в виде ряда;

Y . =Z j.,à "" -Y + г ""

7341 C J 71 Ч где С = +1,— l зависит от процесса слежения за приближением .опредепенной величины к заданному аргументу.

В первом цикпе вычиспения производится прибпижение величиныi к заданному

l аргументу У, т.е. выпопняется решение уравнения Y» Y =О, а затем вычисляются функции ХУ йо следующей системе рекуррентных соотношений:

=r-r. =V.--..а ("")

0 41 14< Чс

4 1 урн Q >. О;

, =ацуп О "1 при U < ()

> =-О Ч = ° ° Z (11>= .у,,2 2(+с) °

141 j4< < 4ф

3 ч « )(у,g (ЯФЧ)

Ю О М =-Х7, =Ю 4q V»+g,g 2<341)

341 41 d 3 1

Сс1- Х

Во втором цикле вычисления производится прибпижение квадрата величинь П,ум1419 ноженное на третий аргумент Ь,к величине

ХУ, попученной в первом цикле вычисления, т.е. выполняется решение управления

ХУ вЂ” ЬО + = 0 по спедующей систеж

3.. рекуррентных соотношений:

U0=Q Q. =g 4,.g <4+1). g XY

141 С Чj ) Й Р у (О =g . щ. = (2 Щ2 д, и у, «gg 2()41)

)41 $41 4 Д ф « . -(+1 (41т рИЮ„Ъ|

Таким образом, в конце второго цикпа вычислений получается требуемая функция.

Структура апгоритмов первого и второго циклов одинакова, за исключением начальных усповий и знаков в первом и третьем соотношениях.

Первое рекуррентное соотношение алгоритма реапиэуется в накопительном регистре 5, сумматоре-вычитатепе 1 .и блоке 9 формирования констант. Второе соотношение реализуется в накопитепьных регистрах 6,8 и сумматоре-вычитатепе 2. Третье соотно599265

Составитель P. Яворовская

Редактор T. Загребельная ТехРед М. БоРисова КоРРектоР С. ШекмаР

Заказ 1416/39 Тираж 826 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, >К-35, Раушская наб., д. 4/5

Филиал ППП Патент", r Ужгород, ул. Проектная, 4 управления, а выход-.со вторым входом первого сумматора-вычитателя, о т л и ч а юш и Й с я тем, что, с целью повышения быстродействия и упрощения устройства, в нем выход регистра сдвига соединен со вто- 5 рым входом второго и первым входом чет» вертого сумматоров-вычитателей, первый выход второго накопительного регистра соединен со вторым входом четвертого сумматора-вычн- атепя, выход которого соединен со вторым входом третьего сумматора-вы итателя.

Источники информации, принятые во внимание при экспертизе

l. "Злектрика, 1.966 т. 39 M 18, с. 30-38, рис. 2

2, Вопросы теории ЗПВМ, вып. 2, Киев, 1968, с. 25-40, рис. 2.