Дискриминатор зоны для аналоговой вычислительной машины

Иллюстрации

Показать всеРеферат

ОП ИСАЙИ вЂ” Е

Союз Советских

Социалистических

Республик (») 588269

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено31.03.75 (21)2118611/24 с присоединением заявки № (23) Приоритет (43) Опублнковано25.03.78. Бюллетень №11. (45) Дата опубликования описания1ч,03.73.

2 (51) М. Кл

Сг 06 (т 7/02

Су 05 В 1/01

Государственный комитет

Совета Министров СССР оо донам изобретений н открмтий (53) УДК681.335 (088.8) Б. С. Смирнов и Е. И. Баду (72) Авторы изобретения (71) Заявитель (54) ДИСКРИМИНАТОР ЗОНЫ ДЛЯ АНАЛОГОВОЙ ВЫЧИСЛИТЕЛЬНОЙ

МАШИНЫ

Изобретение относится к области аналоговой вычислительной техники.

Известно устройство дискриминаторов зоны, которое содержит две мостовые схемы, состоящие из диодов и конденсаторов. В одну из диагоналей каждого моста включены опорные напряжения соответствующей полярности, а к другим диагоналям подсоединены выходы схем сравнения, выполненные на операционных усилителях, на один из входов которых также подсоединено опорное напряжение соответствующей полярности, и через разделительные диоды — входы интегросумматора. Выход интегросумматора через релейные элементы связан со входами схем сравнения (1).

В исходном состоянии конденсаторы мостов заряжены равными, но противоположными по знаку напряжениями, поэтому выходной сигнал с релейного элемента равен нулю. При входном напряжении, выходящим из фиксированной границы зоны, срабатывает одна из схем сравнения, которая нарушает баланс одного из мостов, давая возможность конденсатору этого моста разряжаться на вход интегросумматора.

Известен также дискриминатор зоны, который содержит сумматор, интегросумматор, релейные элементы, нелинейность типа «нечувствительность». Этот дискриминатор обеспечивает выставку зон за счет нелинейности типа «нечувствительность» и релейного элемента. Выход напряжения за пределы зоны нечувствительности вызывает появление сигцала на BxQде интегросумматора (2).

Наиболее близким техническим решением к предложенному изобретению является дискриминатор зоны, содержащий компараторы, первые BxoJbl которых подключены к источнику входного напряжения, вторые входы -- к источникам эталонных напряжений, а выходы соединены между собой и подключены к входным электродам разделительных диодов, исполнительный элемент и логические элементы 11, НЕ (3) .

Недостаток его — отсутствие информации о

15 характере пересечения границ (верхней и нижней) зоны, т. е. происходит ли пересечение при входе в зону нлп нри выходе из нее через одну из границ.

Кроме того, диодные схемы ограничшшя и зоны нечувствительности не стабильны в подло держании выставляемых параметров.

Цель изобретения — повышение точности.

Это достигается путем введения в дискриминатор дополнитель ы: разделительных диодов и счетного триггера, вход которого через первый дополнительный разделительный диод и

599269

Формула изобретения

55 бО последовательно соединенные второй дополнительный диод и логический элемент НЕ подключен к выходным электродам разделительных диодов, один из выходов счетного триггера соединен с исполнительным элементом и с первыми входами первого и второго логических элементов И, другой выход счетного триггера соединен с первыми входами третьего и четвертого логических элементов И, вторые входы второго и третьего логических элементов И связаны с выходом логического элемента НЕ, а вторые входы первого и четвертого логических элементов И подключены к выходному электроду соответствующего разделительного диода, при этом выходы первого и третьего, а также второго и четвертого логических элементов И соединены через диоды.

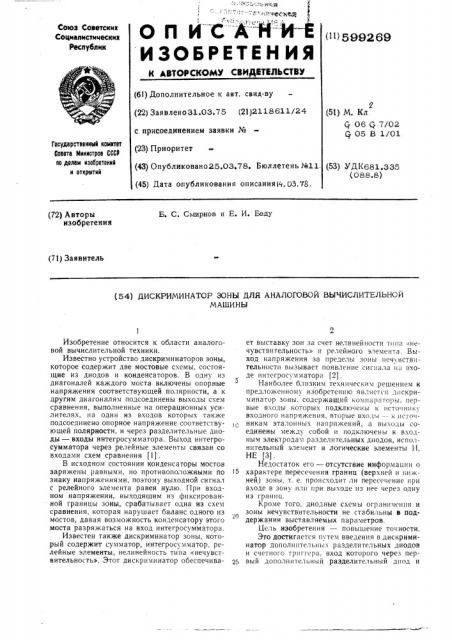

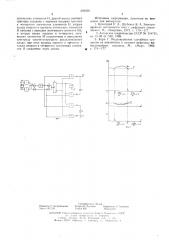

На фиг. 1 представлена блок-схема предлагаемого дискриминатора; на фиг. 2 — импульсы на выходе компараторов при пересечении входным напряжением границ зоны.

Дискриминатор состоит из дифференциально включенных компараторов 1 и 2, на входы которых подсоединены соответственно источники эталонных напряжений U., и U„ и источник входного напряжения Us, . К общему выходу компараторов подсоединена общая точка разделительных диодов " 4. К выходному электроду разделительного диода 3 подсоединен логический элемент НЕ 5. Выход логического элемента НЕ 5 и выходной электрод разделительного диода 4 подсоединены соответственно к входным электродам дополнительных разделительных диодов 6 и 7. Обший выход диодов

6 и 7 подсоединен ко входу счетного триггера 8.

На единичный выход счетного триггера 8 подсоединено исполнительное устройство, например реле 9, а также первые входы логических элементов И 10 и 11. К нулевому выходу счетного триггера 8 подсоединены первые входы логических элементов И !2 и 13. Ко вторым входам логических элементов И 10 и 13 подсоединена обшая точка соединения разделительного диода 4 и дополнительного разделительного диода 7, а ко вторым входам логических элементов И 11 и 12 подсоединен выход логического элемента НЕ 5. Выходы логических элементов И 10 и 12, 11 и 13 соединены соответственно диодами 14 и 15.

Дискриминатор работает следующим образом.

Предположим, что входное напряжение изменяется так, как показано на фиг. 2, тогда при выходе напряжения из зоны, т. е. когда

dU è

">0(U„(0), в момент сравнения с эталонным напряжением, соответствующим верхней границе зоны U„, на общем выходе компараторов

1 и 2 образуется отрицательный импульс, который проходит через разделительный диод 4 и дополнительный разделительный диод 7 на вход счетного триггера 8. При этом на единичном выходе счетного триггера 8 появляется напряжение, приводящее к срабатыванию исполнительного элемента, например реле 9, зафиксировавшего факт выхода входного напряжения 11б„из зоны. Одновременно импульс с выхода разделительного диода 4 поступает на логический

5 о

Эо

40 элемент U 10, на другой вход которого поступает напряжение с единичного выхода счетного триггера. Так как время срабатывания счетного триггера 8 намного больше времени срабатывания логического элемента И, на выходе логического элемента И 10 образуется импульс напряжения, фиксирующий выход входного напряжения U òîëüêî за верхнюю границу зоны.

При возвращении входного напряжения в зону (а " (О и U„) О) на общей точке выхода компараторов образуется положительный импульс U», который проходит через разделительный диод 3, логический элемент НЕ 5 и дополнительный разделительный диод 6 на вход счетного триггера 8. При этом счетный триггер

8 опрокидывается в исходное состояние и отключает реле 9. Срабатывание исполнительного элемента, например реле 9, констатирует факт входа или выхода из зоны, но не фиксирует, какую границу пересекает входное напряжение.

Одновременно импульс с логического элемента НЕ 5 поступает на вход логического элемента И 12, на другой вход которого поступает напряжение с нулевого выхода счетного триггера 8 (триггер находится в опрокинутом состоянии), поэтому до момента опрокидывания триггера в исходное состояние на выходе логического элемента И 12 образуется импульс, фиксирующий факт входа в зону через верхнюю границу входного напряжения. Для пересечения им только верхней границы зоны выходы логических элементов И 1О и 2 соединяются диодом 14.

Аналогично работает устройство, когда входное напряжение пересекает нижнюю границу зоны. Только в этом случае работают логические элементы И 11 и 13. Для пересечения им только нижней границы зоны выходы этих элементов соединяются диодом 15.

Наличие логических элементов в схеме дискриминатора позволяет расширить возможность использования его в устройствах, предназначенных для статистических исследований, в частности в устройствах для определения законов распределения.

Дискриминатор зоны для аналоговой вычислительной машины, содержащий компараторьц первые входы которых подключены к источнику входного напряжения, вторые входы — к источникам эталонных напряжений, а выходы соединены между собой и подключены к входным электродам разделительных диодов, исполнительный элемент и логические элементы И, НЕ, отличающийся тем, что, с целью повышения точности, в него введены дополнительные разделительные диоды и счетный триггер, вход которого через первый дополнительный разделительный диод и последовательно соединенные второй дополнительный диод и логический элемент НЕ .подключен к выходным электродам разделительных диодов, один из выходов счетного триггера соединен с исполнительным элементом и с первыми входами первого и второго

599269! ! (фиг, dt

Составитель С. Белан

Техред О. Луговая Корректор Л. Гриценко

1 и раж 826 Под исное

Редактор Т. Загребельная

Заказ 1417 39

ЦНКИПИ Госуда ствени иo когиигста Cîse-а Минис-; ц CCCP

IIo дела»и изобрoio,.ии ll откр гитин! Зцао.. москва, /К-ЗБ. 1 а (нская нно...ь 1,5

Филиал ППП «Патент», t. Ужгород, 1 и. I 1jloo I illsÿ. -! логических элементов И, другой выход счетного триггера соединен с первыми входами третьего и четвертого логических элементов И, вторые входы второго и третьего логических элементов

И связаны с выходом логического элемента НЕ, а вторые входы первого и четвертого логических элементов И подключены к выходному электроду соответствующего разделительного диода, при этом выходы первого и третьего, а также второго и четвертого логических элементов И соединены через диоды.

Источники информации, принятые во внимание при экспертизе:

1. Кулесский Р. A., Шубенко В. А. Электроприводы постоянного тока с цифровым управлением, М., «Энергия», 1973, с. 175 — 177.

2. Авторское свидетельство СССР № 244731, кл. G 06 G 7/48, 1969.

3. Корн Г. Моделирование случайных процессов на аналоговых и аналого-цифровых вычислительных машинах, М., «Мир», 1968, 10 с. 174 — 177.