Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий зарядно-разрядное устройство, выход которого,соединен с первым входом первого Д-триггера, первьш вход зарядно-разрядного устройства соединен с входами устройства управления, второй вход - с первым выходом устройства управления, а третий вход соединен с выходом вто^ рого Д-триггера и с первым входом элемента И, второй выход устройства управления соединен с первым входом счетчика, второй вход которого соединен с выходом элемента И, второй вход которого соединен с первым входом второго Д-триггера, генератор, третий Д-триггер, отличающий г' -.«fс я тем, что, с целью уменьшения дисперсии преобразования, введены четыре дифференциальных приемника, элемент с прямым и инверс1;[ым входами, причем выход первого Д-триггера через первый дифференциальный приемник соединен с первым входом третьего Д-триггера, выходы которого через дифференциальный приемник соединены со вторым входом второго Д-триггера,"выход генератора через последовательно соединенные элемент с прямым и инверсным входами, третий и четвертый дифференциальный приемники соединен с первым входом второго Д-триггера, а первый вход и выход ' третьего дифференциального приемника соединены соответственно со вторыми входами первого и второго Д-триггеров,2. Преобразователь по п.1, о т - личающийся тем, что, с целью сохранения уменьшения дисперсии преобразования при влиянии внешних дистабилизирующих факторов, дифференциальные приемники, подключенные ко входам одного триггера, выполнены на одном кристалле по интегральной технологии.I(ЛСПсо X) ^

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 H:03 К 1/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 2430528/18-21 (22) 17.12.76 (46) 30.03.86. Бюл. Ф 12 (72) M.Е.Глушковский (53) 681.325 (088.8) (56) Шляндин В.M. Цифровые электроизмерительные приборы. M. Ýíåðãèÿ", 1972, с.92-94.

Патент США В 3.851.258, кл. 340-347, 13.12.73.

- (54) (57) 1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий зарядно-разрядное устройство, выход которого сое- динен с первым входом первого Д-триггера, первый вход зарядно-разрядного устройства соединен с входами устройства управления, второй вход — с первым выходом устройства управления, а третий вход соединен с выходом второго Д-триггера и с первым входом элемента И, второй выход устройства управления соединен с первым входом счетчика, второй вход которого соединен с .выходом элемента И, второй вход которого соединен с первым входом второго Д-триггера, генератор, третий Д-триггер, о т л и ч а ю щ и и —,. с я тем, что, с целью уменьшения дисперсии преобразования, введены четыре дифференциальных приемника, элемент с прямым и инверсным входами, причем выход первого Д-триггера через первый дифференциальный приемник соединен с первым входом третьего Д-триггера, выходы которого через дифференциальный приемник

Соединены со вторым входом второго

Д-триггера, выход генератора через последовательно соединенные элемент с прямым и инверсным входами, третий и четвертый дифференциальный приемники соединен с первым входом второго

Д-триггера, а первый вход и выход третьего дифференциального приемника соединены соответственно со вторыми входами первого и второго Д-триггеров.

2. Преобразователь по п.1, о т л и ч а ю шийся тем, что, с целью сохранения уменьшения дисперсии преобразования при влиянии внешних дистабилизирующих факторов, дифференциальные приемники, подключенные ко входам одного триггера, выполнены на одном кристалле по интегральной тех- нологии °

599747

20

30

Изобретение относится к вычислительной технике и может использовать ся в качестве преобразователя напряжения в код.

Известен аналого-цифровой преобразователь, состоящий из генератора, триггера, ключа и счетчика импульсов.

Однако такое устройство имеет сложное оборудование.

Известен аналого-цифровой преобразователь, содержащий зарядно-разрядное устройство, выход которого соединен с первым входом первого Дтриггера, первый вход зарядно-разрядного устройства соединен с входом устройства управления, второй вход соединен с первым выходом устройства управления, а третий вход соединен с выходом второго Д-триггера и с первым входом элемента И, второй выход устройства управления соединен с первым входом счетчика, второй вход которого соединен с выходом элемента И, второй вход которого соединен с первым входом второго Д-триггера, генератор, третий Д-триггер.

Однако преобразователь имеет значительную дисперсию преобразования.

Цель изобретения — уменьшение дисперсии преобразования.

Для этого в аналого-цифровой преобразователь, содержащий зарядноразрядное устройство, элемент И,счетчик, устройство управления, генератор, три Д-триггера, введены четыре дифференциальных приемника, элемент с прямым и инверсным входами, причем выход первого Д-триггера через первый дифференциальный приемник соединен с первым входом третьего Д-триггера, выход которого через второй дифференциальный приемник соединены со вторым входом второго Д-триггера, выход генератора через последовательно соединенные элемент с прямым и инверсным входами, третий и четвертый дифференциальный приемники соединен с первым входом второго Д-триггера, а первый вход и выход третьего дифференциального приемника соединены соответственно со вторыми входами первого и второго Д-триггеров.

С целью сохранения уменьшения дисперсии преобразования при влиянии внешних дистабилизирующих факторов дифференциальные приемники, подклю" ченные ко входам одного триггера, вы- полнены на одном кристалле по интегральной технологии.

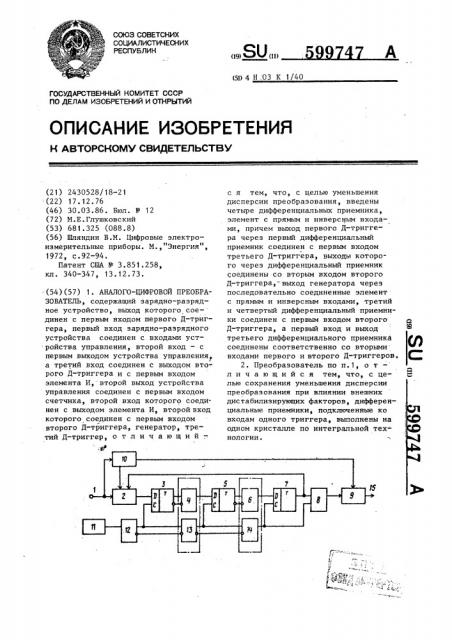

На чертеже дана структурная электрическая схема предлагаемого устройства.

Входная шина 1 через последовательно соединенные зарядно-разрядное устройство 2, первый Д-триггер 3, первый дифференциальный приемник 4, второй Д-триггер 5, второй дифференциальный приемник 6, третий Д-тригL гер 7 и элемент И 8 соединена со счетчиком 9. Выход третьего Д-триггера 7 соединен также с зарядно-разрядным устройством 2. Входная шина 1 через устройство 10 управления соединена с управляющими входами зарядноразрядного устройства 2 и счетчика 9.

Генератор 11 через элемент 12 с прямым и инверсным выходами соединен с

С-входом первого Д-триггера 3. Выходы элемента 12 через третий дифференциальный приемник 13 соединен также с

С-входом второго Д-триггера 5 и четвертым дифференциальным приемником 14, выход которого подключен к С-входу третьего Д-триггера 7 и элементу И 8.

Прямые и инверсные входы всех дифференциальных приемников подключены к соответствующим выходам предыдущих элементов, выход 15 счетчика 9 является выходом всего преобразователя.

Измеряемый импульс поступает на входную шину 1 зарядно-разрядного устройства 2 и заряжает запоминающий конденсатор этого устройства до максимального значения. Одновременно этот же импульс поступает на устройство 10 управления, которое после зарядки конденсатора блокирует вход зарядно-разрядного устройства 2.Далее на Д-вход Д-триггера 3 поступает несфазированный временный интервал, который фазируется с импульсами генератора 11, проходя цепочку Д-триггеров 3, 5, 7. Сфазированный временной интервал с выхода Д-триггера 7 поступает обратно в зарядно-разрядное устройство 2 для включения тока линейного разряда. Кроме того, Дтриггер 7 управляет элементом И 8, который пропускает на счетчик 9 число импульсов, пропорциональное измеряемой амплитуде. После окончания временного интервала по команде с устройства 10 управления код счетчика 9 считывается в накопитель.

599747

Корректор В.Бутяга

Редактор П.Горькова Техред О.Гортвай

Заказ 1626/4 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Для четкой работы преобразовател необходимо, чтобы временной интервал на выходе Д-триггера 7 был хорошо сфазирован с импульсами генератора 11 и поэтому используется много- кратная фазировка на Д-триггерах.

Однако при фазировке на триггере одновременно перепадов обеих полярностей возникает нестабильность, обусловленная тем, что поскольку Д-триггер состоит из двух инверторов, то при запуске в тот инвертор, с которого снимается сигнал на следующий триггер, сигнал может попасть на следующий триггер, а первый триггер не перебросится. Особенно усиливается этот эффект, если окажется, что порог срабатывания триггера ниже по-!

1 рога срабатывания второго инвертора, Нестабильность фазировки приводит К нечетному включению разрядного тока и, как следствие, к повышению дисперсии преобразователя.

Для полного исключения нестабильности между триггерами включен дифференциальный приемник, который при подаче сигнала на один из входов обладает двойным порогом срабатывания. Дифференциальный приемник подключается к триггеру симметрично, S что позволяет фазировать перепады обеих полярностей. Для компенсации дополнительной задержки в цепи фазировки необходимо включить аналогичные элементы в цепи синхронизации.На

10 выходе генератора необходим элемент с прямым и инверсным входами для запуска третьего дифференциального при емника.

15 Для сохранения компенсации задер жек при изменении внешних условий первый и третий, а также второй и четвертый дифференциальный приемники необходимо выполнять попарно на

20 одном кристалле по интегральной технологии.

Включение дифференциальных приемников позволяет сформировать входные сигналы для триггеров фазировки и за счет этого уменьшить дисперсию преобразования.