Полупроводниковое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (,11 60 06I I

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 03.10.7 (21) 2177814/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.03.78. Бюллетень № 12 (45) Дата опубликования описания 30.03.78 (51) М. Кл г G 11С 11!40

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий. (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

В. П. Бастраков и E. Б. Хайтман (71) Заявитель (54) ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано при построении тракта воспроизведения информации запоминающих устройств, накопители которых имеют однопроводную разрядно-считывающую линию.

Известны запоминающие устройства, содержащие накопитель, дешифраторы, формирователи, усилители (1).

Наиболее близким техническим решением к изобретению является полупроводниковое запоминающее устройство, содержащее накопитель, первые шины выборки которого подключены к соответствующим выходам дешифратора строк, вторые — к соответствующим выходам дешифратора столбцов, а нечетные выходные, шины матричного накопителя подсоединены к первым входам дифференциальных усилителей (2).

Недостатки известных устройств состоят в их низкой помехоустойчивости, заключающейся в том, что в таких устройствах не создается разностный сигнал на входах усилителей воспроизведения, а для предотвращения срабатывания усилителей от сигнала с «полувыбранного» блока необходимо введение индивидуальных схем автокоррекции порога срабатывания усилителей.

Цель изобретения — повышение надежности устройства.

Это достигается тем, что в нем четные выходные шины матричного накопителя подключены к вторым входам дифференциальных усилителей.

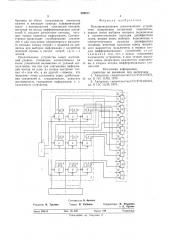

Схема предлагаемого устройства представлена на чертеже.

Устройство содержит дешифраторы столбцов и строк 2, матричный накопитель 3, дифференциальные усилители 4, стробируемые по шине 5 дешифратором 2.

Работает устройство следующим образом.

Дешифраторы столбцов 1 и строк 2 опрашивают одновременно F элементов 6 памяти матричного накопителя 3 на пересечении адреса 1-й строки и 1-ro столбца (F — коэффициент объединения элементов; объединение на чертеже не показано) .

С выходов 7, 8, и 9 на входы 10 и 11 усилителей 4 подаются сигналы, соответствующие хранимой информации.

На одни входы поступают сигналы «1» или

«О» с выбранного по обеим координатам i и 1 элемента 6 памяти, на другие — помехи с «полувыбранного», т. е. опрошенного только по одной из координат.

На первые входы 10 усилителей 4 попадает информация с элементов памяти нечетных строк„на вторые входы 11 — с четных. Помехи с «полувыбранных» элементов памяти, 30 равные «пьедисталу» сигналов «1» и «0» с вы600611

Составитель В, Фролов

Техред Н. Рыбкина

Корректоры: Н. Федорова и Л, Орлова

Редактор И. Грузова

Заказ 258/14

Подписное

Тираж 738

Изд. № 320

Типографии, пр. Сапунова, 2 бранных по обеим координатам элементов памяти и имеющие природу гальванической связи с потенциалами электродов питания, поступая на входы дифференциальных усилителей 4, создают разностные сигналы, несущие только полезную информацию. Соответственно происходит стробирование усилителей 4 для получения однополярного выходного сигнала: сигнал «строб i » подается на усилитель при выборке информации с элементов нечетной строки, а сигнал «строб «+1» — с четной.

Предложенное устройство имеет постоянный уровень отношения сигнал/помеха на входе усилителей независимо от условий эксплуатации, так как при считывании информации всегда на один из входов поступает сигнал «1» или «О», а на другой — помеха, что позволяет точно установить порог срабатывания усилителей и, следовательно, повысить достоверность считывания информации, т. е. надежность устройства.

Формула изобретения

Полупроводниковое запоминающее устройство, содержащее матричный накопитель, 5 первые шины выборки которого подключены к соответствующим выходам дешифратора строк, вторые шины выборки подключены к соответствующим выходам дешифратора столбцов, нечетные выходные шины матрич10 ного накопителя подключены к первым входам дифференциальных усилителей, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства, в нем четные выходные шины матричного накопителя подключе15 ны к вторым входам дифференциальных усилителей.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Хо 377875, 20 кл. G 11С 11/02, 1973.

2. Авторское свидетельство СССР Хо 421045, кл. G 11С 11/40, 1974.