Цифровой преобразователь частоты

Иллюстрации

Показать всеРеферат

,1, Г

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Сотоз Советсиик

Социапистнчесиик

Ресаублин

К АВТОРСКОМУ. СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свих-sy () Заявлено 141125 РИ 2188832/21

У (Ы) а. Кл.

Н 03 К 5/156 с прнсоедннениеии заявки Ю—

Гиир4аритииииыЯ иикитит

Веиити Мииивтрии CCCP ии диии» ииииритииии и 4сирытии (23) Приоритет (43) Опубликовано 3ы378,Бюллетень Щ 12 (53) УЛК 621.374.373 (088. 8) (45) Лата опубликования описания 310378

P2) вторы изобретения

Т.Г.Галамай и В.Б.Пудыкевич (7l) Заявитель (54) ЦИФРОВОИ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ

Изобретение относится к импульсной технике. Известен цифровой преобразователь частоты, содержащий блок управления, реверсивные счетчики, логические элементы И, ИЛИ, генератор опорной. 5 частоты «1 .

Этот преобразователь не обеспечивает необходимой точности.

Наиболее близким по технической сущности к заявленному является преобразователь, содержащий генератор образцовой частоты, выход которого через первый ключ соединен со входом суммирующего счетчика, выходы разрядов которого подключены к первым входам логичЕских элементов И, объединен.ных в два блока, и логический элемент

ИЛИ, первый вход которого соединен с я0 выходом блока управления, а второй через последовательно соединенные элемент задержки и второй ключ соединен с выходом триггера, причем входы триггера и второго ключа соединены с выхо- g5 дом логического элемента ИЛИ, второй выход блока управления соединен со вторым входом первого ключа, а вход блока управления соединен со входом преобразователя j2). 30

Недостатком такого преобразователя является недостаточная точность быстродействия.

Целью изобретения является повьиаение быстродействия.

Для этого в преобразователь, содержащий генератор образцовой частоты, выход которого через первый ключ соединен со входом суммирующего счетчика, выходы разрядов которого подключены к первым входам логических элементов

И, объединенных в два блока, и логический элемент ИЛИ, первый вход которого соединен с выходом блока управления а второй через последовательно соединенные элемент задержки и второй ключ соединен с выходом триггера, причем входы триггера и второго ключа соединены с выходом логического элемента

ИЛИ, второй выход блока управления соединен со вторым входом первого ключа, а вход блока управления соединен .со входом преобразователя, введены два реверсивных счетчика и два делителя частоты импульсов, причем входы Сложение и Вычитание реверсивных счетчиков соединены с дополнительными выходами блока управления, а их входы управления объединены и подключены к выходу логического элемента ИЛИ, вход

600707

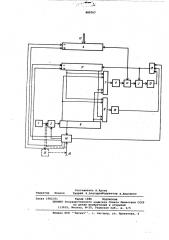

На чертеже приведена структурная электрическая схема преобразователя.

Преобразователь содержит генератор

l5 образцовой частоты 1, ключи 2 и 3, реверсивные счетчики 4 и 5, суммирующий счетчик 6, блоки 7 и 8 логических элементов И, делители 9 и 10 частоты импульсов, триггер 11, элемент 12 задержМ ки, логический элемент ИЛИ 13, блок 1 4 управления и делитель 15 частоты.На вход 16 подан сигнал преобразуемой частоты. сигналов на следуЮщим об30

В исходном состоянии счетчики 5 и 6 и триггер 11 находятся в нулевом состоянии, ключи 2 и 3 закрыты. Блок 14 открывает ключ 2 на время, равное периоду.Т преобразуемой частоты 4 < . В те- З5 чение этого времени импульсы генератора 1 с частотой следования поступают на вход счетчика б. При поступлении на вход счетчика б числа импуль.сов К в течение времени 11=И1/1 сиг- 40 нал со счетчика б поступает на блок 14 ,и импульс с выхода последнего проходит через элемент 13 на вход счетчика

5 и устанавливает его триггеры (не показаны) в единичное состояние. Этот 45 же импульс опрокидывает триггер 11 в единичное состояние, что приводит к отрыванию ключа 3.

60 з З 9

Частота 1, импульсов, поступающих с выхода элемента 13, равна сумме частот, поступающих на ее входы и определяется выражением первого делителя частоты соединен с выходом первого из упомянутых блоков логических элементов И, а его выход подключен ко второму входу триггера, второй делитель частоты включен между третьим входом логического элемента

ИЛИ и выходом второго блока логических элементов И, при этом вторые входы логических элементов И, объединенных в упомянутые блоки, соединены с выхода10 ми разрядов Второго реверсивного счетчика.

Источники питания и чертеже не,показаны.

Работает устройстВо разом.

Логические элементы блоков 7 и 8 являются двухвходовыми. Входы каждого из них в .блоке 8 подключены к выходам одного из триггеров {не показаны) счетчика 5 и одного из триггеров (не показаны) счетчика 6, причем если один из его входов подключен к триггеру младшего разряда счетчика 5, то второй вхОд подключается к триггеру старшего разряда счетчика б и наоборот. Импульс появляется на выходе того из элементов блока 8, который подключен к нахо" дящемуся в единичном состоянии триггеру счетчика 5 и переходящему из нулевого в -единичное состояние триггеру счетчика 6. Средняя частотами следова8 ния импульсов на выходе блока 8, опре. деляемая частотой 1 импульсов, поступающих на вход счетчика 6 и числом

Ц б(4) находящимся в счетчике 5, равна .н,(ц

К коэффициент пересчета счетгде и я хиков °

Импульсы на выходе блока 8 вызываются импульсами, поступающими на вход счетчика б после установки триггеров счетчика 5 в единичное состояние.

Импульсы с частотой 1 поступают

8 на вход делителя 10.

Частота f

Импульсы с частотой 1, поступают через элемент 13 на вход счетчика 5 и вызывают появление импульсов на выходе блока 7.

Элементы блока 7 подключены аналогично элементам блока 8.

Средняя частота f z на выходе блока 7, определяемая частотой f имI пульсов, поступающих с выхода элемента 13 на вход счетчика 5 и числам НЬ(11 находящимся в счетчике б, равна

С,з ЦЬ(Ц » и

П

Импульсы с частотой 1» поступают на вход делителя 9, частота на выходе которого представляется выражением

7 (э Ь() — У

9 . р(, сх ц где о(, — коэффициент деления делителя 9 Импульсы с частотой f)8 с выхода элемента 13 поступают через открытый ключ 3 на вход элемента 12 и далее на второй вход элемента 13. до тех пор, пока импульс с выхода делителя 9 не опрокинет триггер 11 в нулевое состояние и. сигналом с выхода последнего ключ 3 закроется. Перевод триггера 1) в единичное состояние осуществляется очередным импульсом, поступающим на одиночный вход триггера 11 с выхода элемента 13, причем этот импульс не проходит через ключ 3 и тем самым исключается из счета.

Частота импульсов, поступающих с выхода ключа 3, равна разности частот т © и f q импульсов, поступающих с выхода элемента 13 и делителя 9, соответственно

600707 или

4G о К 5 () Л Нь(Всего на счетчике 6 с учетом первых

К» импульсов к моменту времени 1 1 1 поступило количество импульсов иьи) = ft

Окончательное выражение для,з примет вид 4 яМ к И ()

/ о

l5

При работе счетчика 5 в режиме вычитания число в последнем уменьшается с момента времени 1 от величины (Нщ) и в. момент окончания периода Т„частоты т достигнет величины:(+)V

К

При работе счетчика 5 в режиме сложения сигнал со счетчика 6 при пос-туплении на его вход К импульсов поступает на вход блока 14 и импульс с выхода последнего пройдет через эле- д мент 13 на вход счетчика 5 и установит его младший разряд (не показано) в единичное состояние. Дальше устройство будет работать как и в предыдущем случае, но число в счетчике 5 будет З0 увеличиваться.

Записав первоначально в счетчик число щ в прямом или дополнительном кодах, при работе счетчика 4 в режимах сложения и вычитания получим величины обратные выходным характерисI

+с<, Д тикам датчиков: К 1 К „+и

Преобразователь может быть применен и для функционального преобразования высоких частот. Для этого в схему устройства должны быть внесены следующие изменения: выход генератора 1 через делитель 15 подключается ко входу блока 14; преобразуемая частота f „ подается на вход ключа 2.

В преобразователе результат получаем за время, равное периоду преобразуемой частоты при преобразовании низких и V(+) N =, К ° f . + инфраниз- . ких частот, или за время измерения преобразуемой частоты преобразования сред них и высоких частот, т.е. повышается быстродействие.

Формула изобретения

Цифровой. преобразователь частоты, содержащий генератор образцовой частоты, вьход которого через первый ключ соединен со входом суммирующего счетчика, выходы разрядов которого подключены к первым входам логических элементов И, объединенных в два блока, и логический элемент ИЛИ, первый вход которого соединен с выходом блока управления, а второй через последовательно соединенные элемент задержки и второй ключ соединен с выходом триггера, причем входы триггера и второго ключа соединены с выходом логического элемента ИЛИ, второй выход блока управления соединен со вторым входом первого ключа, а вход блока управления соединен со входом преобразователя, отличающийся тем, что, с целью повышения быстродей ствия, в него введены два реверсивных счетчика и два делителя частоты импульсов, причем входы „ Сложение и Вычитание реверсивных счетчиков соединены с дополнительными выходами бло ка управления, а их входы управления объединены и подключены к выходу логи ческого элемента ИЛИ, вход первого делителя частоты соединен с выходом первого из упомянутых блоков логических элементов И, а его выход подключен ко второму входу триггера, второй делитель частоты включен между третьим входом логического элемента ИЛИ и выходом второго блока логических элементов И, при этом вторые входы логических элементов И, объединенных в упомянутые блоки, соединены с выходами разрядов второго реверсивного счетчика.

Источники информации, принятые во внимание лри экспертизе:

1. Патент США Р 3573125,кл.307-251, 11.06.73.

2. Авторское свидетельство СССР

Р 300956, кл. g 01 R 23/02,10.02.69.

600707

Составитель A.Артюх

Редактор Ильина Техред,A.AëàòûðåâÊîððåêòîÐ А.Власенко

Заказ 1902/61 Тираж 1086 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал IlttH Патент, г. ужгород, ул. Проектная,. 4