Устройство для амплитудной дискриминации

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ш16007О9

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 03.12.75 (21) 2195008/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.03.78. Бюллетень № 12 (45) Дата опубликования описания 07.04.78 (51) М. Кл."- Н ОЗК 5/18

Н ОЗК 5/20

Государственный комитет

Совета Министров СССР по делаю изобретений и открытий (53) УДК 621.374.33 (088.8) (72) Авторы изобретения

В. П. Головков и В. А. Фоминов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АМПЛИТУДНОЙ ДИСКРИМИНАЦИИ

Изобретение относится .к импульсной технике и может быть пспользовано в устройствах для измерения параметров электрических сигналов, временных интервалов и д р.

Известно устройство для амплитудной дискриминации, содержащее входной аттенюатор, элементы задержки и подключенные к их выходам элементы сравнения на туннельных диодах (1). Это устройство имеет недостаточную точность вследствие нестабильности времен|ной привязки момента совпадения амплитуд.

Наиболее близким к изобретению является устройство для амплитудной дискриминации, содержащее аттенюатор и элемент задержки, входы которых соединены с источником входных сигналов, г в|ыходы — со входами блока сравнения (2). Однако и это устройство имеет недостаточную точность по тем жс причи нам.

Целью изобретения является повышение точности устройства.

Для этого в устройство введены блок управления и последовательно соединенные иптепратор и амплитудный дискриминатор, причем блок управления включен между входом элемента задержки и одним из входов интегратора, другой вход которого соединен с выходом блока сравнения.

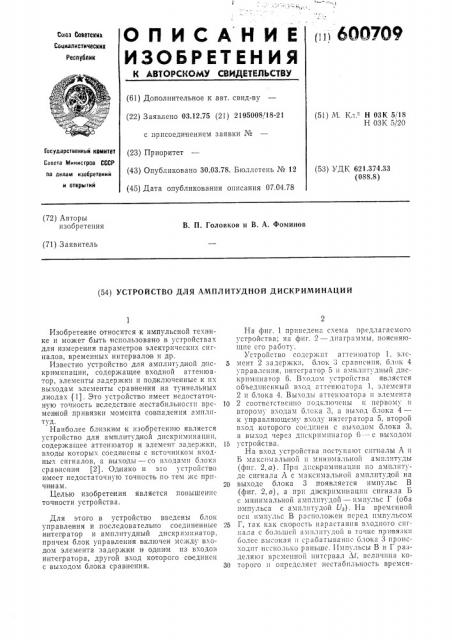

На фиг. 1 пригедена схема предлагаемого устройства; на фиг. 2- — диаграммы, поясняющие его работу.

Устройство содсрж|п аттснюатор 1, элс5 мент 2 задержки, олок 3 сравпсния, блок 4 управления, интегратор 5 и амплитудный дискриминатор 6. Входом устройства является объединенный вход аттенюатора 1, элемента

2 и блока 4. Выходы аттенюатора и элемента

10 2 соответственно подключены к первому и второму входам блока 3, à выход блока 4— к управляющему входу интегратора 5, второй вход которого соединен с выходом блока 3, а выход через дискриминатор 6- — с выходом

15 х стройства

На вход устройства постсупают сигналы А и

Б максимальной и минимальной амплитуды (фиг. 2,a). При дискриминации по амплитуде сигнала А с максимальной амплитудой íа

20 выходе блока 3 появляется импульс В (фиг. 2,в), а при дискриминации сигнала Б с ътинимальной амплитудой — импу Ibc Г (оба импульса с амплитудой U ). На временной оси импульс В расположен псрсд импульсом

25 Г, так как скорость нарастания входного сигнала с большей гмilëiiòóäoé в точке привязки более высокая и срабатыванис блока 3 происходит нссколько раньшс. 11мпхльсы В и Г разделяют временной интервал Л1, величина коЗО торого и определяет нсстаоильность врсмсн600709

НоН привязки. Одновременно входные сигналы поступают на блок 4, с выхода которого поступает сигнал Л или Б в противофазе с входным сигналом (фиг. 2,б).

Блок 4 управления обеспечивает подачу управляющего напряжения на регулируемый элемент интегратора 5. В случае использования в качестве такого элемента варикапа блок 4 является фазоинвертором, который подаст на варикап изменяющееся напряжение смещения обратного направления.

Постоянная интегрирования интегратора 5 меняется за счет изменения емкости интегрирующей цепочки, в которой в качестве переменной емкости используется вари кап. В зависимости от амплитуды сигналов Л и Б рабочая точка на емкостной характеристике варикапа находится либо в области, где емкость варикапа максималына, либо в области, где емкость минимальна. Таким об разом, для сигнала с меньшей амплитудой постоянная интегрирования меньше, чем постояпная интегрирования для сигнала с большей амплитудой, и на выходе интегратора 5 фронт импульса Г затягивается меньше, чем фронт импульса В (фиг. 2, г). Импульс Д или Е поступает на дискриминатор 6 с постоянным уровнем дискриминации. По достижении этими импульсами задан ного уровня дискриминатор

6 формирует импульсы, расстояние между которыми At, всегда меньше интервала At (фиг. 2, г) .

Если параметры RC-цепи интегратора 5 выбраны того же порядка, что и At, амплитуды

U3 импульсов на выходе блока 3 подобраны так, что пересечение фронтов импульсов Д и

Е происходит на относительно линейном участке (импульсы К и И на. фиг. 2, д), а ве5 личина порога дискриминации У,р, совпадает с точкой пересечения импульсов 5К и И, величина Л1 практически сокращается до нуля. При этом нестабильность временного привязки импульсов уменьшается на несколько

10 порядков, что и позволяет повысить точность у стройства.

Формула изобретсн ия

15 Устройство для амплитудной дискриминации, содержащее аттенюатор и элемент задержки, входы которых соединены с источником входных сигналов, а выходы — со входами блока сравнения, отличающееся тем, 20 что, с целью повышения точности устройства, в него введены блок управления и последовательно соединенные интегратор и амплитудный дискриминатор, причем блок управления включен между входом элемента задержки и

25 одним из входов интегратора,, другой вход которого соединении с выходом блока сравнения.

Источники информации, принятые во внимание при экспертизе

1. Лвторское свидетельство СССР №362451, Н ОЗК 5/20, 1971.

2. Материалы симпозиума по наносекундной ядерной электронике. Дубна, 1967, с. 22.

600709 г V, Составитель А. Степанов

Техред Н. Рыбкина

Редактор Н. Громов

Корректор Л. Брахнина

Подписное

Типография, пр. Сапунова, 2

Заказ 355/11 Изд. М 321 Тираж 1080

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, OK-35, Раушская наб., д. 4/5