Устройство задержки

Иллюстрации

Показать всеРеферат

О П И С А Н И Е пц б0073О

ИЗОБРЕТЕНИЯ1

Фовэ Советских

Социалистичеснит

Ресоублнн

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.12.74 (21) 2082126/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.03.78. Бюллетень ¹ 12 (45) Дата опубликования описания 18.04.78 (51) М. Кл.- "Н 03К 17/2Ь

Государстеенный комитет (53) УДК 621.318,562 (088.8) Совета Министров СССР ло делам нэобретеннй и открытий (72) Авторы изобретения

В. Л. Казарин, А. В. Калашников и 3. В. Сурвилло (71) Заявитель (54) УСТРОЙСТВО ЗАДЕРЖКИ

Изобретение относится к области автоматики.

Известны устройства задержки, содержащие операционный усилитель, к неинверсному входу которого подключен источник опорного напряжения, а инверсныи вход через резистор соединен с общей точкой транзисторного ключа и конденсатора и через резистор — с шиной питания (1). Недостатком указанных устройств является недостаточная точность времени задержки, что обусловлено невозможностью сбалансировать входы, так как величина сопротивления на инверсном входе не является постоянной, а зависит от состояния устройства.

Известны также устройства, содержащие транзистор, операционный усилитель, времязадающую КС-цепь, резисторы и диод (zj.

Недостатком таких устройств является то, что временная задержка выражается длительностью выходного импульса. Это делает устройство неудобным в эксплуатации, так как приходится подключать дополнительные элементы, необходимые для преобразования импульса в потенциальный выходной сигнал, задержанный по отношению к входному сигналу на некоторое время, равное длительности импульса.

Целью изобретения является упрощение устройства и повышение его надежности.

Для этого в устройстве, содержащем транзистор, базой, подключенный к входной шине, эмиттером — и оощей шине, а коллектором через резистор — к шине источника питания, операционный усилитель, последовательную

RC-цепь, включенную между коллектором транзистора и инверсным входом операционного усилителя, причем выход КС-цепи через другой резистор соединен с шиной источника

10 питания и через диод — с общей шиной, и резистор, подключенный одним выводом к инверсному входу операционного усилителя, другой вывод указачного резистора соединен с коллектором транзистора.

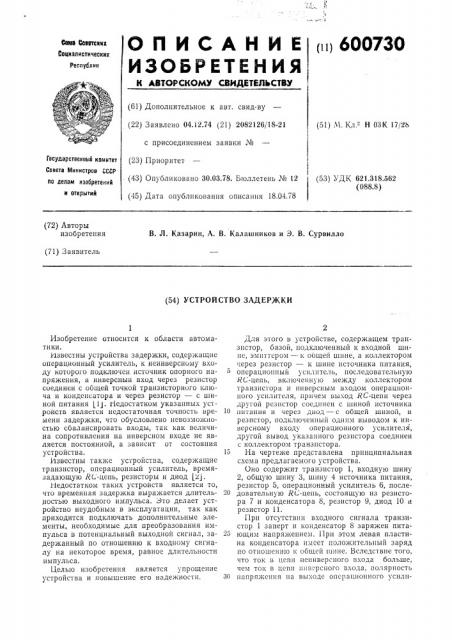

15 На чертеже представлена принципиальная схема предлагаемого устройства.

Оно содержит транзистор 1, входную шину

2, общую шину 3, шину 4 источника питания, резистор 5, операционный усилитель 6, после20 довательную RL, -öåïü, состоящую из резистора 7 и конденсатора Ь, резистор 9, диод 10 и резистор 11.

При отсутствии входного сигнала транзистор 1 заперт и конденсатор 8 заряжен питающим напряжением. При этом левая пластина конденсатора имеет положительный заряд

vo отношению к общей шине. Вследствие того, что ток в цепи неинверсного входа больше, чем ток в цепи инв..рсного входа, полярность зо напряжения на выходе опсрационного усили600730

Составитель И. Радько

Техред Н. Рыбкина

Корректоры; Е. Мохова и Л. Брахнина

Редактор Н. Громов

Заказ 266/15 Изд. № 322 Тираж 1037

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 3(-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2 теля положительна. Когда на входную шину устройства поступает сигнал, транзистор 1 опирается и соединяет с общей шиной левую пластину конденсатора 8, который разряжается. На инверсный вход усилителя 6 поступает отрицательное напряжение от конденсатора

8, а неинверсный вход операционного усилителя подключен к общей шине. В этом случае полярность напряжения на выходе операционного усилителя остается положительной. По окончании разряда конденсатора напряжение сигнала на инверсном входе операционного усилителя 6 станет положительным, что приведет к изменению полярности на выходе усилителя.

Таким образом, изменение полярности на выходе устройства задержки происходит через некоторое время после подачи входного сигнала. Длительность задержки определяется параметрами RC-цепи и соотношением резисторов 9 и 7.

Формула изобретения

Устройство задержки, содержащее транзистор, подключенный базой к входной шине, эмиттером — к общей шине, а коллектором через резистор — к шине источника питания, операционный усилитель, последовательную

RC-цепь, включенную между коллектором транзистора и инверсным входом операционного усилителя, причем выход RC-цепи через другой резистор соединен с шиной источника питания и через диод — с общей шиной, резистор, подключенный одним выходом к неин10 версному входу операционного усилителя, о тл и ч а ю щее с я тем, 1то, с целью повышения надежности, другой вывод указанного резистора соединен с коллектором транзистора.

Источники информации, принятые во внимание при экспертизе

1. Отраслевой стандарт ОСТ 11. Ê0342.003.

20 Дополнение к руководству по применению интегральных микросхем НП0.073.006, с. 179, рис. 26, срок введения 15.06.72.

2. Патент США № 3693030, кл. 307 — 273, 1972.