Двоично-десятичный реверсивный счетчик

Иллюстрации

Показать всеРеферат

!

,}I

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1111 60 0736

Союз Советских

Социалистических

Республик

» Ф,т

/ (61) Дополнительное к авт. свид-ву (22) Заявлено 03.02.76 (21) 2321489/21 с присоединением заявки ¹â€” (23) Приоритет (43) Опубликовано 30.03.78. Бюллетень № 12 (45) Дата опубликова1гня описания 11.04.78 (51) М, Кл. - Н ОЗК 23/00,ь д» Ж"

Государственный комитет

Совета Министров СССР ло делам изобретений н открытий (53) УДК 621.374.32 (088.8) (72) Авторы изобретения

lO. И. Жулин, Н. П. Коновалов и А. В. Филатов (71) Заявитель (54) ДВОИЧНО-ДЕСЯТИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК

Изобретение относится к области автоматики и вычислительной техники.

Известны двоично-десятичные реверсивные счетчики в коде 1-2-4-8, построенные на потенциально-логически.; элементах и содержашис четыре триггера со счетным входом, схемы реверса, сосдинснныс с соотвстствуюшими выходами триггера и с шинами реверса, две схемы блокировки, входы которых соединены с выходами триггеров, а выходы схем блокировки подключены ко входам схем реверса триггеров второго и чствсртого разрядов, при этом импульсный вы. од триггера первого разряда соединен со входом схемы реверса триггера четвертого разряда;(1).

Однако быстродействие этого счетчика Огр а н ичсно.

Известен также двоично-десятичный рсвсрсивный счетчик в коде 1-2-4-8, содержащий чстырс, по числу разрядов, счетных триггера, по четыре элемента И в суммарном и разностном канала,, ка кдый из которых соединен, соответственно, первым входом с единичным или нулевым выходом триггсра соответствующего разряда, четыре элемента ИЛИ, входы псрвого из которых являются входами суммарного и разностного каналов счетчика, входы други., элементов ИЛИ подключены к выходам элементов И соответствующих разрядов суммарного и разностного каналов, третий вход элсмента ИЛИ четвертого разряда соединен с выходом элемента И IcTBcpTQIQ разряда суммарного канала, язляющимся выходом этого канала счстчика, à выходы всех элементов

И. IИ подключены к счст1ым входам триггеров соотвстствую1ц11х разрядов, элсмсiIT 111., входом соединенный с выходом элемента И третьего разряда разностного канала, а выходом — со входом элсмснта И четвертого раз10 ряда разностного канала, выход которого является выходом разностного канала счетчика, Олокируюший элсмснт И, первым вxoäoм подключенный к нулевому выходу триггсра четвсртогo разряда, вторым — к шине разрсшс1 ния счета разностного канала, а выходом сос gllliclliiblII с блокиру1ошнми входами тригге ров второго и третьего разрядов, причем ши11а разрешения счета разностного канала присоединена ко вторым входам элементов И

20 трех первых разрядов разностного канала, шина разрешения счета суммарного канала соединена со вторым входом каждого из чстырсх элементов И суммарного канала, нулевой выход триггсра четвертого разряда подклю25 чсн к третьему входу элемента И псрвого разряда суммарного канала (2).

Для этОГО счстч и к а та кжс х ар актс13 но нсдоCTBTO 111OC ObICTPOQCilCTBIlC

С нс, Iblo по13ы111сн1111 бьlстрод IIcTlIIIII 13 дво30 II (Ilo- cslTII IHblli pcBc 3снвпый cLIcT IIII B 1 Оде

600736

ЗО

1-2-4-8, содсржатций четыре, по числу разрядов, счетных триггера, по четыре элемента И в суммарном il разпостном каналах, каждьш из которых соединен соответственно, первым входом с единичным или нулевым выходом трпьч ера соотвстств) югцсго разряда, четыре элемента 1ЛИ, входы первого из которых являются входами суммарного и разностно .о каналов счетчика, входы других элементов ИЛИ подключены к выходам элементов И cooTIICTствующих разрядов c)ììàðíoãо и разностного каналов, третий вход элемента И, !И четвертого разряда соединен с выходом элемента 1! четвертого разряда суммарного канала, являющийся выходом этого канала счетчика, а выходы всех элементов ИЛИ подключены к счетным входам триггеров соответствующих раз. рядов, элемент НЕ, входом соединенный с выходом элемента И третьего разряда разностного канала, а выходом — со входом элемента И четвертого разряда разностного канала, выход которого является выходом разностпого канала счетчика, блокирующий элемент И, первым входом подключенный к нулевому выходу триггера четвертого разряда, вторым -- к шине разрешения счета разностного капала, а выходами соединенный с блокирующими входамп триггеров второго и третьего разрядов, причем шина разрешения счета разпостного канала присоединена ко вторым входам элементов И трех первых разрядов разностного канала, шина разрешения счета суммарного канала присоединена ко вторым входам каждого из четырех элементов И суммарного канала, нулевой выход триггера четвертого разряда подключен к третьему входу элемента И первого разряда суммарного канала, введена схема компенсации времени переключения триггера первого разряда, входом подключенная к выходу элемента ИЛИ, установленного на входе счетчика, а выходом сосдllнснпая со входамп всех элементов И каждого разряда как суммарного, так и разностного каналов, исключая выходной элемент И четвертого разряда разностного канала и блокирующий элемент И, причем единичный выход триггера первого разряда подключен к четвертым входам элементов И второго и трстьсго разрядов разностного канала, единичный выход триггера второго разряда подключен к пятому входу элемента И третьего разряда суммарного канала, а его нулевой выход подк;почен к пятому входу элемента И третьего разряда разностного канала и к третьему входу блокирующего элемента И, нулевой выход триггера третьего разряда подключен к четвертому входу блокирующего элемента И.

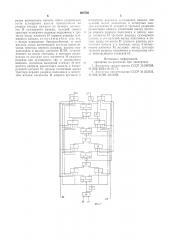

На фиг, 1 представлена структурная схема двоично-десятичного реверсивного счетчика; на фиг. 2 — диаграммы, поясняющие работу данного счетчика.

Предлагаемый счетчик содержит четыре счетных триггера 1 — 4, четыре элемента И 5 — 8 суммарного канала, элементы И 9 — 11 разностного канала, блокирующий элемент И 12, элемент И 13, четыре элемента ИЛИ 14 — 17, элемент 1-1Е (инвсртор) 18 и схему 19 компенсации времени переключения триггера первого разряда, прсдставляющу ю сооой липино задс )жки, сигнал на Выходс контро тя задержан относительно сигнала на шинах 20, 21 суммарногo;i разностного каналов на время, равное (0,8 — 0,9) времени псрскл|очсния триггера 1.

Счетчик содержит также шины 22, 23 разрешения счета и выходы 24, 25 суммарного и разностного каналов.

На вход счетчика по одной из шин 20 или

21 поступают тактовые IIxii льсы (см. фш, 2,Q). В 3TQ врсмя триггер 1 нмс T состояния, представленные на фиг. 2,6. Переключение этих состояний происходит Ilo отрицательным перепадам входного сигнала с задержкой на время т,— время переключения триггера 1. арлем Hòом И 5 в суммарном канале или элементом И 9 в разпостном канале производится определение совпадений входных импульсов с импульсами, поступающими с выхода триггера

Введение схемы 19 приводит к совпаденшо на элементах И 5 и 9 импульсов, ITocT)пающих с выхода триггера 1, с импульсами, поступающими с выхода схемы 19, задержанными cl о на 0,8 т, относительно входных сигналов.

На вы: оде других схем совпадения при этом формпр ются IIvlll) льсы, представленные на фпг. 2,г.

Формула изобретения

Двоично-десятичный ревсрсивный счетчик в коде 1-2-4-8, содержащий четыре, по числу разрядов, счетных триггера, по четыре элемента И в суммарном и разностном каналах, каждый пз которых соединен, соответственно, перовым входом с единичным илп il)ëcâûì вы«одом триггера соответствующего разряда, четыре элемента ИЛИ, входы первого из которы являются входами суммарного и разностного каналов счетчика, входы других элементов ИЛИ подключены к выходам элементов И соответствующих разрядов суммарного и разностного каналов, третий вход элемента

ИЛИ четвертого разряда соединен с выходом элемента И четвертого разряда суммарного канала, являющимся выходом этого канала счетчика, а выходы всех элементов ИЛИ подключены к счстным входам триггсpo}s соответствующих разрядов, элемент НЕ, входом соединенный с выходом элемента и третьего разряда разностного канала, а выходом — со входом элемента И четвертого разряда разностного канала, выход которого является выходом разностного канала счетчика, блокирующий элемент И, первым входом подключенный к нулевому выходу триггера четвертого разряда, вторым — к шине разрешения счета разностного канала, а выходом соединенный с блокирующими входамп триггеров второго и третьего разрядов, причем шина разрешения счета разностного канала присоединена ко вторым входам элементов И трех первых раз600736 рядов разностного канала, шина разрешения счета суммарного канала присос:пшена ко вторым входам каждого из четырех элементов И суммарного канала, нулевой выход триггера четвертого разряда подключен к третьему входу элемента И первого разряда суммарного канала, отличающийся тем, что, с целью повышения быстродействия, в него введена схема компенсации времени переключения триггера первого разряда, входом подключенная к выходу элемента ИЛИ, установленного па входе счетчика, а выходом соединенная со входами всех элементов 1Л каждого разряда как суммарного, так и разностного каналов, исключая выходной элемент И четвертого разряда разностного канала и блокирующий элемент И, причем единичный выход триггера первого разряда подключсн к четвертым входам элементов И второго третьего и гствсртого разрядоз суммарного канала, его нулевой вы. од: одключси к четвертым входам элементов 11 второго п третьего разрядов разностного капала, единичный выход триггс5 ра второго разряда подключен к пятому вхо.IA элемента И третьего разряда суммарного !

;!IIBла, а сго нулевой выход подключен к пятому входу элемента И третьего разряда разностиого канала и к третьему входу б.зокиру10 ницего элемента И, нулевой выход триггера трстьсго разряда подключен к четвертому входу блокирующего элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР ¹ 358788, Н 03К 23/24, 01.07.71.

2. з,вторскос свидетельство СССР ¹ 353352, 11 031 21/00, 13.10.69.

600736 с

) (!

Составитель Л. Лемуткии

P(дактор Н. Ванииева Тскрсд Н. Рыбкина Корректоры: Е. Хмелева и Л. Орлова

Заказ 353, !4 1!зд. ¹" 325 Тираж 1087

11ПО Государственного комитета Совета Министров СССР во делам изобретений и открытий

113035, Москва, Ol(-35, Раушская наб., д. 4/5

Подписное

Типография, нр. Сапунова, 2