Делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

(tt! 600738

ОП И(:АН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСИОМУ СВМДЕТЕЙЬСТВУ

Со се Советских

Социалистических

Ресиублик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.03.76 (21) 2332382/18-21 с присоединением заявки М— (5l) it<. 1хл. - Н 03К 23, 02

Совета Министров СССР по делам иэосретений и открытий (43) Опубликовано 30.03.78. Бюллетень эхе 12 (45) Дата опубликования описания 11.04.78 (53) УДК 621.374 44 (088.8) (72) Авторы изобретения

Л. И. Ильченко и 1О. И. Кузьмин (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

Государствеииый комитет (23) Приоритет

Изобретение относится к вычислительной технике.

Известен делитель частоты следования импульсов, содержащий симметричный триггер, источник смещения и источник запускающих импульсов (1J. Запирание открытого транзистора происходит через вентильные схемы, которые управляются состоянием триггера, что является дополнительным фактором уменьшения быстродействия триггера, так как при уменьшении выходного напряжения триггера за счет емкостной нагрузки нарушается логика работы входных цепей.

Целью изобретения является повышение быстр од ей ств ия делителя.

С этой целью в делитель частоты следования импульсов, содержащий симметричный триггер, источник смещения и источник запускающих импульсов, введены резисторы, диоды и резистивный делитель напряжения, при этом между зажимами источника запускающих импульсов и каждым из выходов симметричного триггера включена цепь, состоящая из последовательно соединенных резистора и двух согласно-включенных диодов, точка соединения которых через конденсатор подключена к входу симметричного триггера, а между каждым входом упомянутого триггера и средней точкой резистивного делителя напряжения, включенного между источником запускающих импульсов и источником смещения, включен третий диод. !

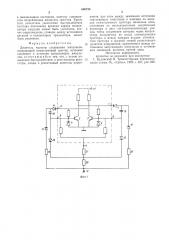

la фпг. 1 представлена принципиальная электрическая схема делителя частоты следо5 вания импульсов; на фпг. 2 — временные диаграммы, иллюстрирующие работу устройства.

Делитель частоты содержит симметричный триггер на транзисторах 2 и 3 и диодах 4 и

5, имеющий единичный 6 It нулевой 7 выходы

Ip и единичный 8 и нулевой 9 входы, источник эапц скающttx импу чbcов (зажим 10), источник смсщенпя (зажим 11).

Между зажимом 10 и выходом 6 триггера 1

)5 включена цепь, состоящая из послсдоьательно соединенных резистора 12 и согласно-BI(;Itoченных диодов !3 и 14, а между зажимом 10 и выходом 7 триггера 1 — цепь, состоящая из последоьательно соединенных рсзпстора 15 и

20 согласно-включенных диодов 16 It 17. Кроме того, разнополярные выводы диодов 13 и 14 также соединены посредством конденсатора 18 со входом 9 триггера 1, а разнополярные выводы диодов 16 и 17 также соединены через

25 конденсатор 19 со входом 8 триггера 1. Между зажимом 10 и зажимом 11 находится резисторный дслптсль напряжения, состоящий из резисторов 20 и 21, причем средняя точка этого рсзистивного делителя напряжения соеди30 непа через диоды 22 и 23, прямосмсщасмыс

600738

35 источником смещения, с входами 9 и 8 триггера 1 соответственно.

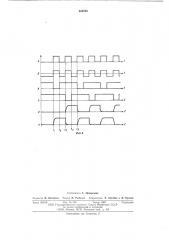

1!а фиг. 2 приняты обозначения: а — запускающие импульсы И„„; б — импульсы в средней точке омпчсского делителя на резисторах

20 и 21; в — импульсы на выходе 7 трштера 1; г — импульсы на выходе 6 триггера 1; д — диоды напряжений на конденсаторе 18;

e — диоды напря>кений на конденсаторе 19.

В рассматриваемом случае запускающие импульсы Upas имеют сква>кность, равную двум (см. фиг. 2,а). Резистивный делитель напряжения на рсзисторах 20, 21 смещает нулевой уровень входных импульсов, и с выхода его уже снимаются двухполярные импульсы (см, фнг. 2,б).

В исходном состоянии оба транзистора 2 и

3 триггера 1 выключены отрицательным напря>кением, поступающим со средней точки омичсского делителя на резисторах 20, 21 (см. фиг. 2,в и г). Конденсаторы 18 и 19 предположительно разря>кены (см. фиг. 2,д и а).

B момент времени t!, когда приходит положительный фронт первого запускающего импульса,оба конденсатора 18 и 19 начпнаютзаря>каться по цепям: конденсатор 18 — базаэмнттер транзистора 2 — зажим 10 — резистор 12 — диод 13 — конденсатор 19 — базаэмиттер транзистора 3 — зажим 10 — резистор

15 — диод 16. В результате транзисторы 2 и 3 начинают приоткрываться. Но, вследствие разброса параметров транзисторов, один приоткрывается чуть быстрее, второй медленнее.

Предположим, быстрее приоткрывается транзистор 3. Тогда, в момент, когда потенциалы коллектора транзистора 3 и конденсатора 18 сравняются, он начинает перехватывать ток, который раньше заряжал конденсатор 18. Если он успел немного зарядиться, то разряжается по цепи: конденсатор 18 — диод 14— транзистор 3 — диод 4. Транзистор 3 полностью открывается, транзистор 2 — закрывается. Рсгснеративный процесс происходит очень быстро, так что можно считать, что в момент времени 1, транзистор 3 открывается, транзистор 2 закрывается, запоминающий конденсатор 18 остается разряженным, конденсатор

19 заряжается с постоянной времени taap.

В момент времени t2 по окончании действия первого запускающего импульса на оба транзистора подается запирающий отрицательный потенциал через открытые диоды 22 и 23.

Транзистор 3 закрывается. Диоды 13, 14, 16, 17 закрыты, конденсатор 18 — разряжен, а конденсатор 19 — заряжен.

B момент времени 1з приходит второй положительный запускающий импульс. Диоды 22 и 23 запираются. Так как конденсатор 18 был разряжен, диод 13 открывается и течет ток заряда конденсатора 18 по,цепи: конденсатор

18 — база — эмиттер транзистора 2 — зажим

10 резистор 12 — диод 13. Этим зарядным током открывается транзистор 2. Потенциал его коллектора падает, диод 17 открывается, и конденсатор 19 разря>кается по цепи: кон10

15 p0

>7Д

65 денсатор 19 — диод 17 — транзистор 2 — диод

5. Итак, в момент времени 11 (см. фиг. 2) транзистор 2 открывается, транзистор 3 закрывается, конденсатор 18 заряжается, конденсатор 19 разряжается, причем постоянная времеH!! разряда тр;,р мала, так как сопроп илснис цепи разряда невелико.

В момент времени 14 открь!ваются диоды 22 и 23 (аналогично моменту времени 4), и транзистор 2 закрывается. Диоды 13, 14, 16, 17 заперты. Конденсаторы находятся в предыдущем состоянии: конденсатор 18 заряжен, конденсатор 19 разряжен.

В момент времени t5 прихода очередного положительного запускающего импульса диоды 22 и 23 закрываются. Так как конденсатор 19 был разряжен, открывается диод 16 и течет ток заряда конденсатора 19 по цепи: конденсатор 19 — эмнттср-база транзистора

3 — зажим 10 — резистор 15 — диод 16, открывая транзистор 3. Потенциал коллектора транзистора 3 падает, открывается диод 14, и конденсатор 18 разряжается, а конденсатор 19 заря. кается. B последующие моменты времени процессы повторяются.

Если импульсы на выходе трп1тера имеют длительность -с и достигают амплитуды 0,67

Uar»;, то входной сигнал имеет скважность, равную двум.

Так как положительные полупериоды выкодных импульсов B обоих случаях равны т„, а сква>кность известна, увеличение быстродействия оценивается соотношением

fnpeg a l 1 г

1,о пред 1 где fnpei.! — предельная частота ного триггера 1

taped. — предельная частота делителя, Т, — период выходных импульсов симметричного триггера i, Т вЂ” период выходных импульсов делителя.

Следует отметить, что при использовании коротких запускающих импульсов быстродействие увеличивается еще больше (в пределе его увеличение стремится к двум).

Из диаграмм работы предлагаемого устройства (см. фиг. 2) видно, что наиболее ответственная фаза работы делителя (выключение включенного транзистора) происходит мощным входным запускающим импульсом независимо от состояния триггера. Это устраняет указанный недостаток известных схем (когда прп уменьшении выходного сигнала нарушается логика работы входных цепей), что позволяет схеме надежно функционировать при повышенном быстродействии. Указанное преимущество особенно важно при работе триггера на емкостные накопители, где нужно обеспечить полный заряд и разряд конденсатора.

Как видно из временных диаграмм (см. фиг. 2), скважность выходных импульсов делителя более или равна четырем, и большую часть времени транзисторы 2 и 3 находятся

600738 в выключенном состоянии, поэтому уменьшается потребляемая мощность триггера. Кроме того, вследствие увеличения быстродействия триггера постоянная времени заряда конденсатора нагрузки может быть увеличена, значит сопротивление, стоящее между источником питания и коллектором транзистора, может быть увеличено, Формула изобретения

Делитель частоты следования импульсов, содержащий симметричный триггер, источник смещения и источник запускающих импульсов, отличающийся тем, что, с целью повышения быстродействия, в него введены резисторы, диоды и резистивный делитель напряженпя, при этом между зажимами источника запускающих импульсов и каждым из выходов симметричного триггера включена цепь, состоящая из последовательно соединенных

5 резистора и двух согласно-включенных диодов, точка соединения KQTopbIx через конденсатор подключена ко входу симметричного триггера, а между каждым входом упомянутого триггера и средней точкой резистивного

10 делителя напряжения, включенного между источником запускающих импульсов и источником смещения, включен третий диод.

Источники информации, принятые во внимание при экспертизе

15 1. Будинский Я. Транзисторные переключающие схемы. М., «Связь». 1965, с. 327, рис. 236, 600738 Ф 5

Риа, 2

Составитель T. Афанасьева

Редактор Н. Ванииева Тсхрсд H. Рыбкина Корректоры: E. Хмелева и Л. Орлова

Подписное

Заказ 353/16 Изд. М 325 Тираж 1087

EEEIO Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5Ê-35, Рауптскгя наб., д. 4/5

Типография, пр. Сапунова, 2