Устройство для измерения запаздывания случайного сигнала

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республик

П"Ж С А--Н И Е (11} 603.698

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДВТВЙЬСТВУ (61) Дополнительное и авт. свнд-ву(22) Заявлено14.07.75 (21) 2156108/18-24 с присоединением заявки №(2З) Приоритет(43) Опублиновано05.04.78.Бюллетень ЭЬ 13 (45) Дата опубликовании описания:13.03,78 (5I} M. Кл, QO6 7 15/36

Гаоударотееиеай «ом«тет

Вовета М««лотре« СССР

«о делам «зебр«те««й я от«Рыт«й (53} УДК 681.317. . 757 (088.8) (72} Авторы изобретения

И. И. BoziKoB, В, В. Мотов, A. П. Токарев и В. К.,Семенычев.

Куйбышевский политехнический институт им. В. B. Куйбышева

Pl) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЗАПАЗДЫВАНИЯ

СЛУЧАЙНОГО СИГНАЛА

Изобретение относится к специализированным средствам вычислительной техники, предназначенным для измерения во времени случайных сигналов, и может быть использовано при обнаружении сигналов на фоне помех, B радиодальнометрии, в измерительной технике при экспериментальном исследовании случайных сигналов и s других случаях.

Известны устройства, предназначенные т для измерения запаздывания случайного сиг-10 нала, содержащие умножители, вычнтающее устройство и систему регулируемого запазд,ывания (1)и. (2), Однако блок регулируемого запаздывания, входящий в состав известных устройствтл для входного широкополосного аналогового сигнала, весьма труден в аппаратурной реализапии при высоких требованиях к амплитудно-частотным и фазо-частотным характеристикам. При этом, чем больше диа- ра назон регулирования и задержка, тем больше аппаратурные погрешности.

Наиболее близким техническим решением к известному является устройство для измерения запаздывания случайного сигнала со- З

2 держащее первый и второй умножитель, первый вход которого соединен с первым входом устройства, вычитающий блок, блок управления и блок регулируемого запаздывания, управляющий вход которого через блок управления соединен с выходом вычитающего блока, информационный вход - с вторым входом устройства, а первый и второй выходы - с вторыми вхдодами соответственно первого и второго умножителей, выходы которых через фильтры нижних частот соединены соответственно с первым и вторым входами вычитающего блока, в которых первый вход первого умножителя подключен к первому входу устройства.

Однако s этом известном устройстве наблюдается большая методическая погрешность, обусловленная необходимостью предварительного определения знака задержки сигналов и возможным выходом на ложный экстремум в случае колебательного характера взаимокорреляциойной функции исследуемых процессов.

Белью изобретения является повышение точности измерений.

601698

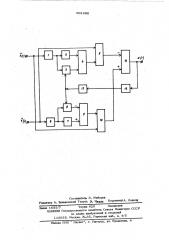

3 .Цля этого в устройство введены сумматор н второй вычитаюший блок, ° выходы которых подключены к вторым входам со ответственно первого и второго умножителей, выходы которых соединены соответственно с первым и вторым. входамц первого вычитаюшего блока; блок усреднения, вход которого соедицен с выходом первого вычитаюшего блока, а выход — с входом блока управления; первый и третий фью . ® ры нижних частот, входы которых подключены соответственно к первому и второму входам устройства, а выходы - к входам соответственно второго и четвертого фильтров нижних частот, выходы которых подклю; к чены к первым входам соответственно сумматора и второго вычитакецего блока; первый и второй линейные преобразователи, вхо. ды которых соединены с выходами соответственно первого и третьего фильтров нижних частот, выходы -.с вторыми входами соответственно сумматора к второго вычитаюшего блока, а управгппошие входы - с выходом блока управления, и второй вход устрой, ства соедииеН с первым входом первого: ум цбжителя.. На чертеже приведена структурная электричесКая схема устройства..:

Устр©йство для измерения запаздывания я«p случвфйго сигнала содержит последователь;цо са®дииЪниые фильтры нижних частот (ФНЧ) ..i. и 2,:.s ФНЧ 1 соединен с. первым входом устройства, а выход. через линейный преобрааов тель 3 подклк>чен к второму входу Зв суммами .ера 4, выход ФНЧ.2 подключен не-. аасредотаеиаэ к первому входу сумматора 4, ащц «атервгр подключен к второму входу умножителей 5, К второму входу устройства подклвчеий первый вход умножится 5 и по,40 щедодетельио соединенные ФНЧ.6 и ФНЧ 7..

ЭыходФНЧ 8 через лниейный преобразоватепь 6 подключен к второму входу вычитающего блока

9, а выход ФНЧ 7 - непосредственно к пер@ему адщу вычитающего блока .8, подключен "в нога к второму входу умножителя 10, первый вход которого подключен к первому входу устройства, а выход - к второму входу вычитаюшего блока 11, первый вход „которого соединен с, выходом умножнтеля 5. Вы-50 ход вычитающего блока 11 через последовательно соединенные блок для усреднения

12, блок для управления 13 подключен к управляющим входам линейного преобразователи 3, линейного преобразователя 8 и вы- 55 ходу устройства.

Устройство работает следующим образом.

На первый вход устройства поступает сигнал % (Ф ), а на второй вход — сигнал

3(t)

4

В результате обработки входных сигналов в группах блоков, состоящих из ФНЧ и линейных преобразователей (1, 2, Э и 6, 7, 8), на первые входы сумматора 4 и вычитаюшего блока 9 поступят сигналы соответственно:

CO о — Ъ(«>«И-«>ае и Г

1 " Ф где 9(t) © - импульсная переХ ходная характеристика ФНЧ 1, 2, 6, 7 а на вторите .уходы — соответственно:

«и>>и«>х(+- «>ж, о и.

«<«> js(s>4<-ú>àñ, 9

me Ь Ж . — коэффициент преобразования линейного преобразователя 3 (или 8).

В результате преобразования этих си палов в блоках 4 и 8 и перемножения с входными сигналами в умножителях 5 и 10 на выходе вычитакяцего блока 11 будет действовать сигнал:

OO

1 г o o м(м* — у йж) x(t)Y(+- 5 йс.Т о.

-кИ) И )хи)ЧИ-гМС1 г

- — ) й(с):к(мхи-z ucо

-к(Ф) Ъ (С)УИ) х(Ф с)я . (1) о

С выхода вычитающего блока 11 сигнал поступает на вход блока для усредне ния 12, и далее.на вход блока для управления 13.

В установившемся режиме сигнал на входе блока для управления 12, являющийся оценкой математического ожидания сигнала вычитаюшего блока 11, будет равен нулю, т.е.:

>«t stt>1. - àíò>ì «ó>÷ ü-z>1dzT о

-«нфт>««>.х1л\чн-х>1асо

Щ. . - — СЬ (С)М(Ф() Х(4-С))ЮТ >

0 рр

-кИ) 4(смt Y(+)х(-ъЯи о. (2) 601698

Из этого соотношения можно получить выражение для коэффициента преобразования линейного преобразователя:3(8) s новившемся режиме:

+ФФ 5 ю. "

t (31 Т е

Если принять сигнал Y(t) равным 1й

Y(w) ex(a+ ), где: Гу - время задержки;

C - постоянный коэффнпиент, то нз выражения (3) получим: 15

a(t ) а —

@ °

Таким образом, коэффициент преобразования линейного преобразователя 3 (8) в установившемся режиме определяет измеря«

20 емое время запаздывания случайного сигнала.

Повышение аппаратурной точности в щедложеняом устройстве достигается за счег того„что в нем вместо блока регулируемого запаздывания применена группа более простых блоков, состоящая из двух линейных преобразователей и четырех фильтров нижних частот, которые могут быть реали 3e зованы " с высокой адпаратурной точностью в широком динамическом диапазоне., .Кроме того, как видно из описания принципа работы устройства, оно свободно от мето- дического недовтатка, присущего известным устройствам - необходимости априорного

З знания знака времени запаздывания.

Формула изобретения

Устройство для измерения запаздывания 4О случайного сигнала, содержащее первый и второй умножители, первый вход которого соединен с первым входом. устройства, вычитаюшнй блок и блок управления, о т л нч а ю щ е е с я тем,. что, с целью ловы« щения точности измерений, оно содерхыт сумматор и второй вычитмощнй блок, сумматор и второй вычитающий блок, выходы которых подключены к вторым входам с оответственно первого и второго умножителей, выходы которых соединены соответственно с первым и вторым входами первого вычитающего блока;:. блок усреднения,,вход которого соединен с выходом первого вычитакипего блока, а выхвд - с входом блока-управления; первый и третий фильтры нижник частот, входы которых подключены соответственно к ° первому и второму входам устройства, а выходы - к входам. соответственно второго и четвертого фильтров нижних частот, выходы которых подключены к первым входам соответственно сумматора и второго вычитаюmего блока; первый и второй линейные преобразователи, входы которых. соединены с выходами соответственно aepaoro и третьего фильтров нижних частот, выходы - с вторыми входами соответственно сумматора и второго вычитающего блока, а управляющие .входм» с выходом блока управления, и второй вход устрайства соединен с Первым входом первого умножителя.

Источники информапии, принятые во внивепие при экспертизе:

- 1. Жовинский В. Н. н Арховский В. Ф.

Коррелядионные устройства, М., 1974, с. 217-22О.

2. Догановский C. А. и Иванов В. А.

Устройства запаздывания и нх применение в автоматических системах, 1966,, с. 177-267.

Э; Авторское свидетельство СССР

И. 226959, кл. QO6 г 15/34, 1969.

601698

Составитель Л. Майоров

Редактор А. Зиньковский Техред Э. мужик КорректофА.- Лакн щ

Заказ 1655(7 Тираж 826 Подписное

ЦНИИПИ Государственного комйтета Совета Министров СССР по делам изобретений и открытий

11ЗОЗ5, Москва, Ж-35,.Раушская наб., д. 4/5

Филиал ППП " Патент, г. Ужгород, ул. Проектная, 4