Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

(61) Дополнительное к авт. евид-ву (22} Заявлено 23.01.76(21) 2318880/18-24 с прнсоедннеиием заявкн № (23) Приоритет (43) Опубликовано 05-„04. 78 Бтоллетень №,1 3 (45} Дата опубликования описанои 13,03.78

2 (5е) М. Кл.

Q 11 С 27/00

Гвсудврственныб немнтет

Севетв Меннстрва CN) ве денем нзоеретенн» н стержнй (53) Д < 681.327.66 (088,8) (72) Авторы мвобретеяня 4. A. Врякин H. П- Вашкевич и В. Ф. Говоров (7е) Заявитель

Пензенский попитехнический институт (54) АНАЛОГОВЩ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к области вычиснитепьной техники, Известно анапоговое запоминающее устройство, содержашее входной, ключевой и выходной каскады (lj . в

Ванное устройство, обпадая бойьшим временем хранения, имеет йизкое быстродействие.

Наиболее близким к изобретению является анапоговое запоминаюшее устройство, содержашее входной дифференциальный каскад, кпючевой каскад и выходной каскад, выходы которого соединены с первым и вторым входами входного дифференциального каскада, а вход — с накопительным энементо м j2).

Недостаток этого устройства закпючается в низком быстродействии.

Белью изобретения является повышение быстродействия анапогового запоминаюшего устройства.

Дпя достижения поставпенной цепи предложенное устройство содержит согласуюший каскад, тпелитель> напряжения и двуппечевой эмиттерный повторитепь. Первые входы сог-

2 пасуюшего каскада подкпючены к выходам входного дифференциапьного каскада, второй вход - к ключевому каскаду, а выход через делитель напряжения — к двуплечему эмиттерному повторитепю, выход которого подкпючен к накопительному эпементу.

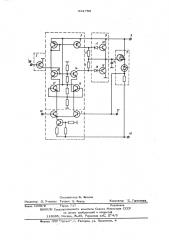

На чертеже представлена принципиальная схема у=тройства.

Устройство содержит входной дифферен- циапьный каскад 1, ключевой каскад 2, выходной каскад 3, накопитепьный элемент 4, согласуюший каскад 5, делитель напряжения, содержаший резисторы 6, 7е двуппечий эмиттерный, повторитель 8 и источни» ки йитаюшего напряжения 9, 10, транзисторы 11-14 дйоды 15, 16. Согласующий касе кад содержит транзисторы 11-14, а эмыттерный повторитель 8 — транзисторы 15, 16 и диоды 17, 18.

Потенциалы напряжения на базах транзисторов согпасуюшего каскада 5 выбраны таким образом, что при выключенном ключевом каскаде 2 транзисторы 11, 12 от-. крыты, а транзисторы 13 и 14: закрыты.

При выключении ключевого каскада 2

3 зисторы 11, 12 закрыты, а транзисторы

13 14 открыты.

Устройство переходит в режим "хранения" при включении ключевого каскада 2, а в режим слежения при его выключении.

Устройство работает следующим 9бразом.

При подаче на вход 19 изменяющего аналогового напряженки входной дифференциальный каскад 1 усиливает его и через включенные транзисторы 13, 14 по сигналу с входа 20 напряжение подается на делитель напряжения. Выходное напряжение с делителя подается на накопительный элемент 4 и на выходной каскад 3; который производит соглааование уровней напряжения делителя напряжения и выходного сигнала.

При этом напряжение на элементе 4 изменяетса вслед за изменением входного сигнала.

При режиме слежения за входным сиг налом можно отметить два этапа работы устройства. Для первого этапа, когда входной сигнал изменяется с небольшой скоростью или постоянный, характерным явля ется соблюдение неравенства. авэо О л I < "б. "Оо где „и 3 - токи через резисторы 6, 7 соответственно; номинальное сопротивление резисторов 6, 7

Π— напряжение отпирания транзисторов

15 или 16, 0 — падение напряжения на открытом дио*.о де 17 или 18.

При этом элемент 4 перезаряжается разностным током 3„- 3 и транзисторы 15, 16 закрыты.

Во время второго этапа, когда уровень напряжения на входе и выходе 21 устройства ненамного отличаются один от другого или когда входной сигнал изменяется с большей скоростью, справедливо одно из неравенств

lJ ° (U +U или л "Б эо- ао.

При этом открывается транзистор 15 либо 16, и элемент 4 перезаряжается соответственно током 1 или

2 . 3, О Б.. з.o еU à

1, Д Ь

-3

1 I РФР 1 р - . г ) 2 р А p д

us., u . ,(1 тр А р а где Р - динамическое сопротивление переТР хода база-эмиттер открытого транзитора 15 или 16, Р— динамическое сопротивление диода;

А

- статический коэффициент усиления по току транзистора 15 или 16.

Таким образом, работая„в нелинейном режиме, транзисторы 15, 16 позволяют

2О увеличить ток, перезаряда накопительного элемента 4 и тем самым значительно повысить быстродействие всего устройства.

Формула изобретения

Аналоговое запоминаюшее устройство, содержашее входной дифференциальный каскад, ключевой каскад, выходной каскад, ЗО выходы которого соединены с первым и вторым входами входного дифференциального каскада, вход — с накопительным элементом,отличаюшееся тем, что, с целью повышения быстродействия

З устройства, оно содержит согласуюший каскад, делитель напряжения и двуплечий эмиттерный повторитель, причем первые входы согласуюшего каскада подключены к выходам входного дифференциального каскада, второй вход — к ключевому каскаду, а выход через делитель напряжения — к двуплечему эмиттерному повторителю, выход которого подключен к накопительному зле менту.

Источники информации, принятые во вни. мание при экспертизе:

1. Авторское свидетельство СССР

¹ 334572, кл. Я 06 9 7/03, 1970.

2. Патент Японии № 49-21744, 50 кл. Н 03 К 7/02, 1974.

601759

Составитель В. Фролов

Редактор Л. Утехина . Texpen 3. Фанта

Корректор .С. Гарасиняи, Филиал ППП "Патент», r. Ужгород, ул. Проектная, 4

Заказ 1659/9 Тираж 7 17 Подлисное

ЦНИИПИ Государственного комитета Совета Министров СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д;- 4/5