Устройство для возведения в квадрат двоичных чисел

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 602941

>; (61) Дополнительное к авт. свид-ву(22) Заявлено 16.07.76 (21) 2398566/18-24 с присоединением заявки №вЂ” (23) Приоритет(43) Опубликовано 15.04.78.Бюллетень № 14 (45) Дата опубликования описания 2Î 03.7-8

2 (5!) М, Кл.

С» 06 F 7/38

Гасударственный комитет

Совета Министров СССР

- по дедам изооретений и открытий (53) УДК 681.325 (088.8) (Т2) Авторы изобретения В. И.. жабин, В. И. Корнейчук, В. В. Макаров и В. П. ТаРасенко (71) Заявитель Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ

ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к области вычислительной TcxHHKII и может быть применено в цнс)>ровых вычислительных машинах и устройствах, пос|роснных на основе больших интегральных схем. г, Известны устройства для возведения в квадрат двоичных чисел (1), построенные либо на основе множительных устройств. либо на основе других схем вычислительной техники. В некоторых сл чаях для ускорения вычислений примсняются матричные устройства. Эти устройств» являются устройствами параллельного действия, т. е. для вычисления квадрата числа необходимо наличие всеx цифр операнд;l.

Наиболсс близким техническим решением к данному изобретению является устройство для возведения в квадрат двоичных чисел, содержащее дня сумматора, группу элементов ИЛИ, регистр (2). Недостатком его является низкое быстродействие.

Цельк> изобретения является повышение быстродействия.

Это достигается тем, что предлагаемое устройство содержит элементы задержки и блок анализа разрядов, информационные в, оды ксторого соединены с выхс>дами первого сумматора, управляющие входы -- с первой управляюгцей шиной, выходы с>локя анализа разрядсв соединены с выходами устройства. вторая управляющая шина сосд шена с управляющими входами первого сумматора и регистра, управляющие входы которого через первый и второй элементы задержки соединены соответственно с первыми и вторыми информационными входами устройства и второго сумматора, а выходы которого подключены к одним входам группы элементов И, 1И, другие входы которой соединены с выходами регистра. я выходы группы элементов 111И вЂ” со входами первого сумматора, информационные входы второго сумматора соединены с выходами регистра, и тем. что блок анализа разрядов содержит элемент ИЛИ, элемент 1.1 — HE, два элемента И, причем первые и вторые входы элементов И 1И и И вЂ”,НЕ подключены соответственно к первому и второму информационным. входам блока анализа разрядов, выходы элементов ИЛИ и

11 — НЕ подключены соответственно к первым входам элементов И. вторые входы которых подключены к третьему информационному Входу блока анализа разрядов, третьи входы — с управляющими входами блока анализа разрядов, выходы элементов 11 подключены к выходам блока анализа разрядов.

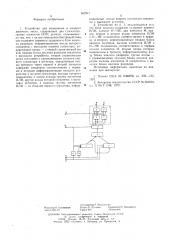

Ня чертеже показана схема предлагаемого устройства.

602941 з

В устройство входят сдвигающий регистр

1, сумматор 2, блок элементов ИЛИ 3, сумматор 4, блок анализа разрядов 5, элемент

ИЛИ 6, элемент И вЂ” НЕ 7, элементы И 8, 9, элементы задержки 10, 11, информационные входы 12, 13, управляющие входы 14, 15 и выходы 16, 17.

Сдвигающий регистр 1 и сумматор 2 содержит и разрядов, где и — разрядность представления операнда. Сумматор 2 имеет знаковый разряд.

Выходы сдвигающего регистра 1 связаны со входами сумматора 2 и блока элементов ИЛИ 3.

Выходы сумматора 2 подключены ко вторым входам блока элементов ИЛИ 3. Блок элементов ИЛИ 3 содержит (и + 1) элементов ИЛИ.

Выход первого разряда сдвигающего регистра

1 связан со входом второго элемента ИЛИ, выход второго разряда сдвигающего регистра

1 подключен ко входу третьего элемента ИЛИ и т. д., а выход каждого i-rb разряда сдвигаюшего регистра 1 связан со входом (i+1)-го элемента ИЛИ. Выход каждого i-го разряда 2Е сумматора 2 связан со вторым входом i-го элемента ИЛИ. Выходы блока элементов ИЛИ

3 подключены ко входам сумматора 4, причем выход каждого i-го элемента ИЛИ связан со входом (i+5)-го разряда сумматора 4, который содержит (п+5) разрядов. Блок анализа разрядов 5 содержит элемент ИЛИ 6, элемент

И вЂ” НЕ 7, элемент запрета 8 и элемент И 9.

Входы знакового разряда и разрядов целой части сумматора 4 подключены ко входам блока анализа разрядов 5. Выходы второго и З0 третьего разрядов сумматора 4 (разряды целой части) подключены ко входам элемента ИЛИ 6 и элемента И вЂ” HE 7. Выход элемента ИЛИ 6 связан со входом элемента И 8. Выход элемента И вЂ” HE 7 подключен ко входу элемента И 9.

Выход знакового разряда сумматора 4 связан с инверсным входом элемента И 8 и элемента И 9.

Устройство работает в соответствии со следующим алгоритмом

1.М; =2К;1+х;(2 Х;- +х;2 )

Х, =X;i+x;2

2. 1,еслибы;(— 1 у = О,если — 1 <М; (!

1, если 1Ч; )1

З.R; = N; — 2у;, где х; — очередной разряд операнда (х, !1,0, 1, ), 45

Х; — содержимое сумматора 2 (в нем записано известное к этому времени значение операнда, (Х) - !. у, — очередной разряд вычисляемой функции (у; Е(1,0,1}), R,. содержимое сумматора

i-го цикла вычислений, N; — содержимое сумматора 4 в i-ом цикле вычислений, i = 1,2,..., и + 3.

4 к каналч

В исходном состоянии в старшем разряде ы сдвигаюшего регистра 1 записана единица, в остальных разрядах — нули. В сумматорах

2, 3 запис аны нули.

Вычисление функции осуществляется в (и + 3) циклах. каждый из которых состоит из трех тактов. В первом такте (каждого i-ro цикла) на информационные входы 12, 13 поступает значение очередного разряда операнда (операнд поступает, начиная со старших разрядов) . При этом, если единичный сигнал поступает на информационный вход 12, это свидетель. ствует о том, что очередной разряд операнда численно равен 1. Если единичный сигнал поступает на информационный вход 13, очередной разряд операнда численно равен единице..Если же единичный сигнал не поступает ни на один из информационных входов 12, 13, это свидетельствует о том, что очередной разряд операнда численно равен нулю.

Если единичный сигнал поступает на информационный вход 12, содержимое сумматора

2, сдвинутое вправо на один разряд, вычитается из содерж имо о сумматора 4.

Если единичный сигнал поступает на информационный вход 13, содержимое сумматора 2, сдвинутое на один разряд вправо, суммируется с содержимым сумматора 4.

Время, на которое сигнал задерживается в элементах задержки 10, 11, должно быть больше времени, необходимого на эту операцию. Затем сигнал с информационных входов

12, 13 снимается, появляется сигнал на выход» одного из элементов задержки 10, 11. Если единичный сигнал появляется на выходе элемента задержки 10, содержимое сдвигаюшего регистра 1 вычитается из содержимого сумматора 2, и этот же код, сдвинутый на два разряда вправо вычитается иь содержимого сумматора 4. Если единичный сигнал появляется на выходе элемента задержки 11, содержимое сдвигающего регистра 1 суммируется с содержимым c).÷ìàòoðîâ 2, 4.

Во втором такте по управляющему сигналу, поступающему на управляющий вход 14, производится выдача информации на выходы устройства. Если единичный сигнал появится на выходе 16, это свидетельствует о том, что очередной разряд требуемого значения функции численно равен 1, если единичный сигнал появит. ся на выходе 17, очередной разряд треоуемог0 значения функции численно равен 1. Если единичный сигнал не появится ни на одном пз выходов 16 17, очередной разряд требуемого значения функции численно равен О.

В третьем такте по управляющему сигналу, поступающему на управляющий вход 15, производится сдвиг информации в сумматор» 4 и сдвигающем регистре 1.

После этого в сумматоре 4 образуется значение R,, а в (i+ 1) -м разряде сдвигающего регистра 1 будет записана единица. На этом оканчиваегся очередной цикл вычислений. В результате (п+3) циклов вычислений на выходах 16, 17 последовательно разряд за разрядом формируется требуемое значение функции

f(X) =Х 2, представленное избыточным двоичным кодом с цифрами 1,0,1 в каждом разряде. Причем, в резулыате выполнения (и+3! циклов, результат получается симметрично округленным.

60294

Формула изобретения

1b П

Составитель P. Яворовская

Техрел О. Луговая Корректор П.Макаревич

Тираж 826 Подписное

Релактор Н. Каменская

Заказ 1851/45

Ш1ИИПИ государственного комитета Совета Министров СССР но ледам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4,5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

1. Устройство для возведения в квадрат двоичных чисел, содержащее два сумматора, группу элементов ИЛИ, регистр, отличающее- 5 ся тем, что, с целью повышения быстродействия, оно содержит элементы задержки и блок анализа разрядов, информационные входы которого соединены с выходами первого сумматора, управляющие входы — с первой управляющей шиной, выходы блока анализа разрядов соединены с выходами устройства, вторая управляющая шина соединена с управляющими входами первого сумматора и регистра, управляющие входы которого через первый и второй элементы задержки соединены соответственно с первыми и вторыми информационными входами устройства и второго сумматора, выходы которого подключены к одним входам группы элементов

ИЛИ, другие входы которой соединены с выходаь|и регистра, а выходы группы элементов

ИЛИ вЂ” со входами первого сумматора, инфор1

G мационные входы второго сумматора соединены с выходами регистра.

2. Устройство по п. 1, от1ичающееся тем, что блок анализа разрядов содержит элемент

ИЛИ, элемент И вЂ” НЕ, два элемента И, причем первые и вторые входы элементов ИЛИ и И вЂ” НЕ подключены соответственно к первому и второму информационным входам блока анализа разрядов, выходы элементов ИЛИ и

И вЂ” НЕ подключены соответственно к первым входам элементов И, вторые входы которых подключены к третьему информационному входу блока анализа разрядов, третьи входы— с управляющими входами блока анализа разрядов, выходы элементов И подключены к выходам блока анализа разрядов.

Источники информации, принятые во внимание при экспертизе:

1. Патент США М 3780278, кл. 235 — 165, ! 971.

2. Авторское свидетельство СССР Хо 364934, кл. G 06 F 7/38, 1972.